vcs仿真的一个诡异错误

时间:10-02

整理:3721RD

点击:

很简单的代码, EEBinBuf 赋值的地方只有下面这个block

always_ff @(posedge SCL4IP)

begin:EEDinBuf_block

if (!OSC_EN) begin //not programing IP.

if (STP_SR && STP_S && !READ) begin

EEDinBuf[BITSEL] <= EEDBI;

end

end

end

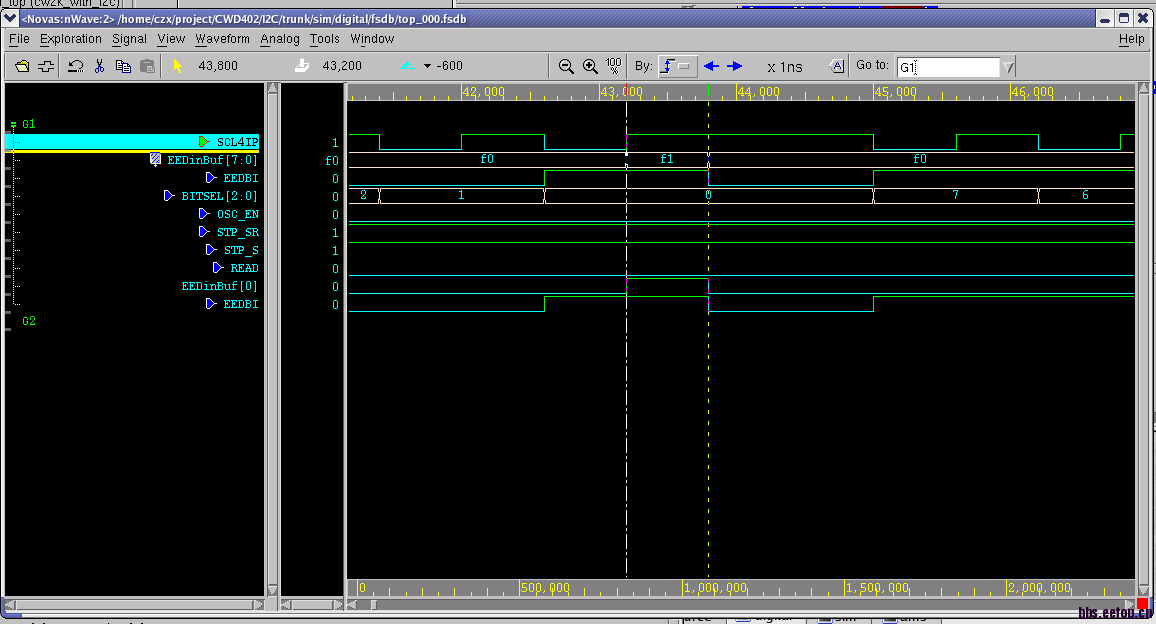

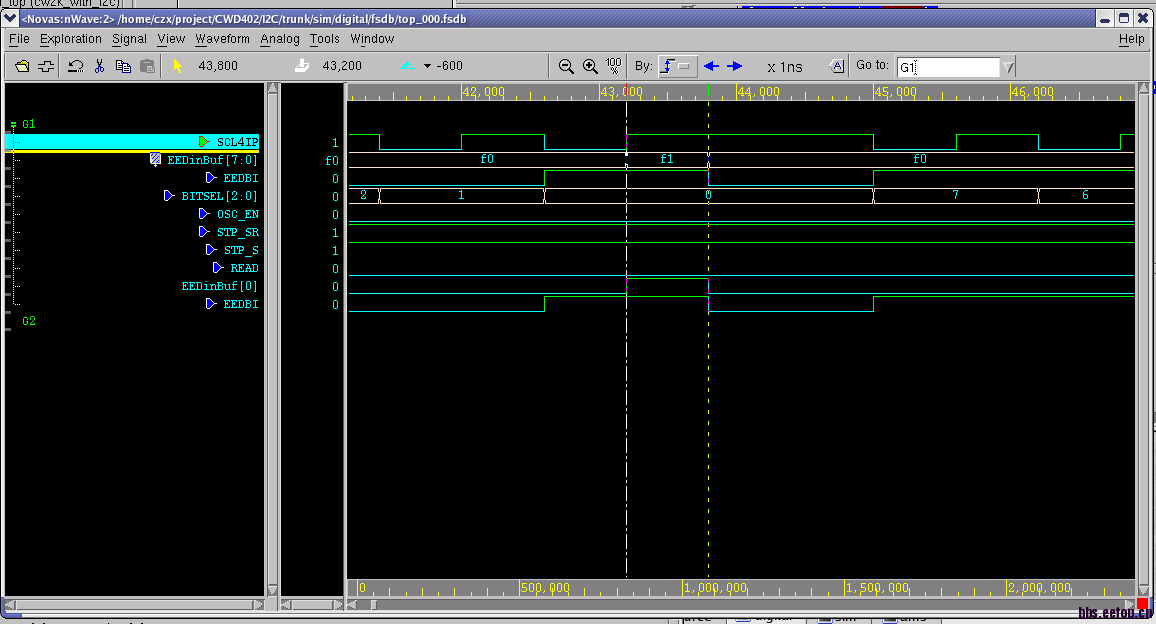

其中 osc_en,stp_sr,stp_s, read这几个信号一直保持不变,在白色光标线出, SCL4IP的上升沿,EEDinBuf改变正常,但是诡异的是,

在黄色光标处,EEDinBuf的最低位居然跟着EEDBI发生改变了,这个时候SCL4IP 一直=1,按理不能变啊。

请大家讨论讨论,看看这个是个什么可能。

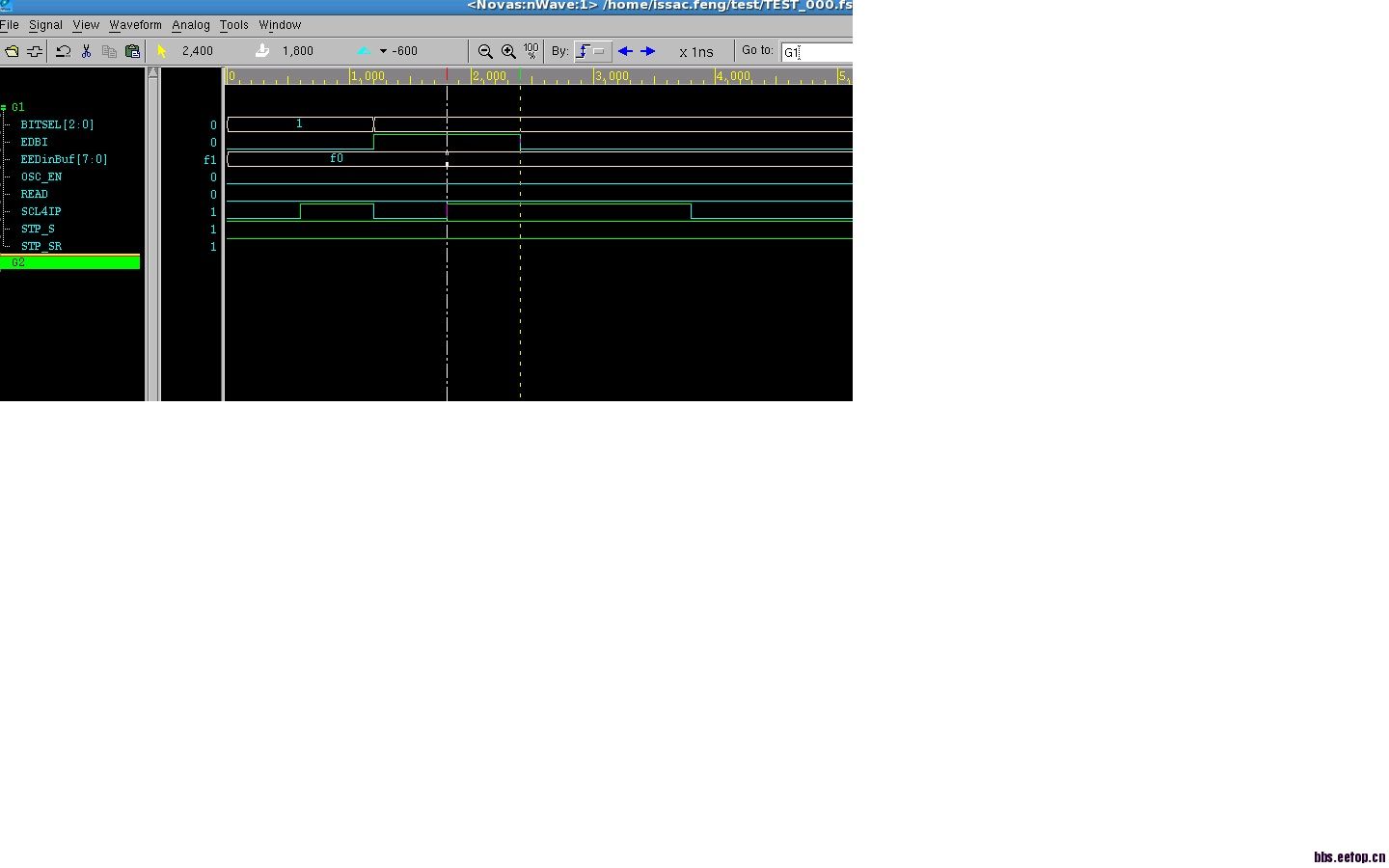

试过assign SCL4IP_DB = #50 SCL4IP, 然后always @(posedge SCL4IP_DB) .... 就没有问题了。

看波形这上面也没有什么glitch 啊。 vcs有什么控制glitch的相关选项么?

谢谢大家

always_ff @(posedge SCL4IP)

begin:EEDinBuf_block

if (!OSC_EN) begin //not programing IP.

if (STP_SR && STP_S && !READ) begin

EEDinBuf[BITSEL] <= EEDBI;

end

end

end

其中 osc_en,stp_sr,stp_s, read这几个信号一直保持不变,在白色光标线出, SCL4IP的上升沿,EEDinBuf改变正常,但是诡异的是,

在黄色光标处,EEDinBuf的最低位居然跟着EEDBI发生改变了,这个时候SCL4IP 一直=1,按理不能变啊。

请大家讨论讨论,看看这个是个什么可能。

试过assign SCL4IP_DB = #50 SCL4IP, 然后always @(posedge SCL4IP_DB) .... 就没有问题了。

看波形这上面也没有什么glitch 啊。 vcs有什么控制glitch的相关选项么?

谢谢大家

可以尝试换个VCS版本试试,或使用ncverilog试一试

根据你给出的代码,我在ncverilog上测试是没有问题的,也许是条件不完全一致

建議刪除VCS RUN目錄下的生成的中間文件再重新跑一次.

谢谢答复经检查是 scl4ip有glitch