关于源时钟和门控时钟间的相位差的问题

时间:10-02

整理:3721RD

点击:

且不考虑设计是否合理,我用门控时钟,有100M的时钟,产生一个50M的时钟,这2个时钟之间的相位差取决于什么因素?只是Tco吗?

请各位大侠明示!多谢多谢!

请各位大侠明示!多谢多谢!

用门控时钟的话,尽量通过产生一个使能信号来控制哈

是的,应该是要通过时钟使能信号来控制的,不过我想知道2个时钟直接的相位差的影响因素,呵呵~

就看CLOCK-GATING是什么样的架构了,以及CLOCK PIN的位置

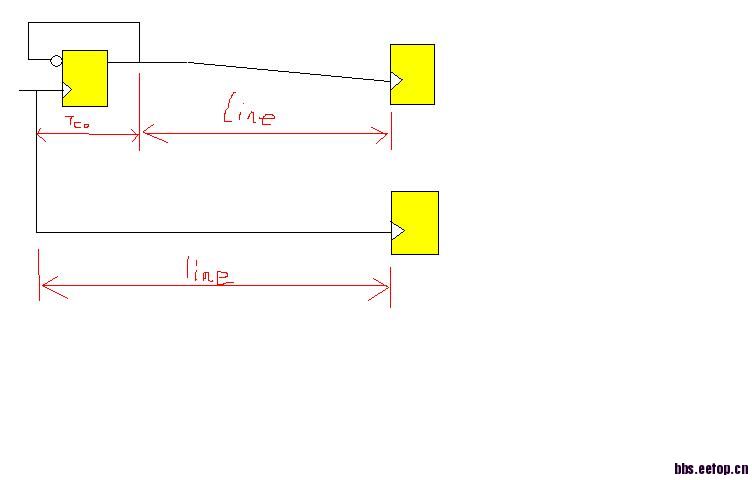

你看这个电路那些因素会导致延时,那些就是因素:

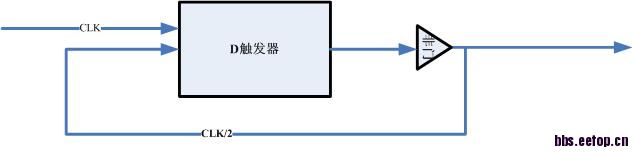

这个是二分频电路,不能算门控时钟。对于这个电路来说,当然就是DFF的传输时间了

门控时钟主要是FREE-LATCH和BASED-LATCH的两类

Tco + 走线延迟 吧

FPGA内部走线延迟很严重,而且难调整。

ASIC可计算且可调整。