请教这个程序主要是实现什么功能的啊

时间:10-02

整理:3721RD

点击:

module dso_sinc_mult(clk,reset, x_in,datain,endata_out,sum);

module dso_sinc_mult(clk,reset, x_in,datain,endata_out,sum);/*y_out1,y_out2,y_out3,y_out4,y_out5,y_out6,y_out7,y_out8,y_out9,y_out10,*/

input clk,reset;

input signed [7:0] x_in;

input signed [7:0] datain;

output signed [16:0] sum;

output endata_out;

//output signed [16:0] y_out1,y_out2,y_out3,y_out4,y_out5,y_out6,y_out7,y_out8,y_out9,y_out10;

//reg signed [16:0] y_out1,y_out2,y_out3,y_out4,y_out5,y_out6,y_out7,y_out8,y_out9,y_out10;

reg [4:0] count;

reg endata_out ;//, ena_io

reg signed [16:0] dataout; // temp sum

reg signed [7:0] ibuf [0:10];

reg signed [16:0] sum; // temp sum

parameter IL = 9;

/////////////////////////////////////////////////////////////////////////////

always @(posedge reset or posedge clk)

begin : FSM // Control the system and sample at clk rate

if (reset) // Asynchronous reset

count <=5'b0;

else begin

if (count ==5'b10011)

count <=5'b0;

else

count <= count +5'b1;

end

end

/*always @(posedge clk)

begin

if (count == 0)

ena_io <= 1;

else

ena_io <= 0;

end*/

always @(posedge clk)

begin // set the enable signal for the TAP lines

case (count)

1,3,5,7,9,11,13,15,17,19: endata_out <= 1;

default : endata_out <= 0;

endcase

end

always @(posedge clk)

begin : INPUTMUX

integer I;

begin

ibuf[0] <= x_in;

for (I=0; I<=IL; I=I+1)

ibuf[I+1] <= ibuf[I];

end

end

///////////**************************************************************/////////////

always @(posedge clk) // Compute sum-of-products for f0

begin : OUPUTMUX

reg signed [16:0] p [0:9];

integer I;

begin

dataout = p[0];

for (I=0; I<=IL; I=I+1) // Infer L+1 multiplier

begin

p[I] = ibuf[I]*datain ;

dataout= dataout + p[I];

sum <= dataout ;

end

end

end

//******************************************************************************************//

endmodule

怎么没人看看呢

哪位仁兄帮帮忙,看看哦

8位有符号数的乘法....

PS:这是学软件的人写的代码吧....

不是乘加啊?卷积

这个代码不是RTL级的,你要这个代码干什么?测试吗

的确不是RTL的,看起来象是测算验证用的代码

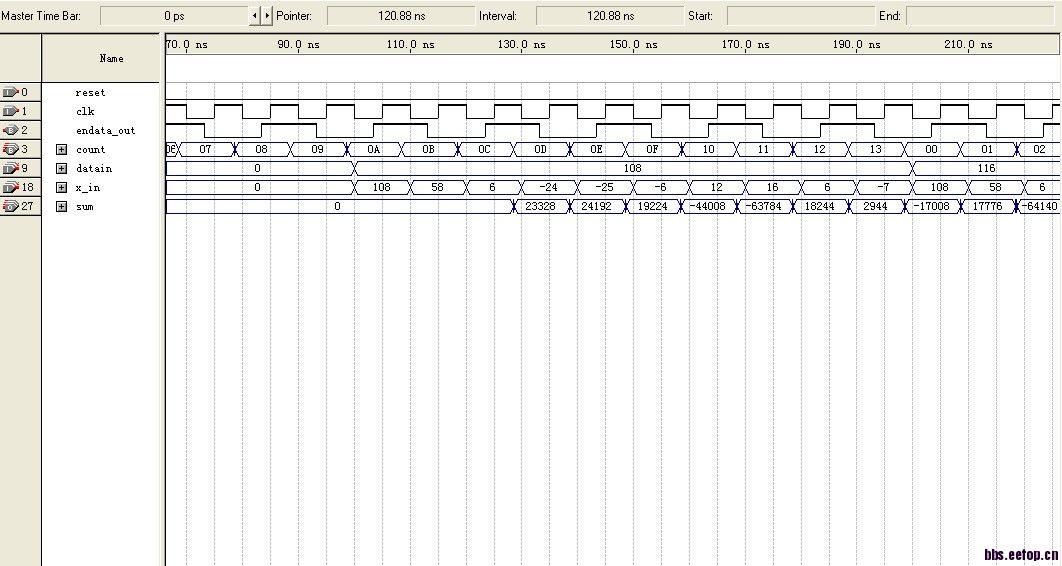

验证我做的东西啊。其实我是想做个插值算法。看见别的书上有个这样的代码,然后修改了一点。但是仿真的时候好像结果不太对。