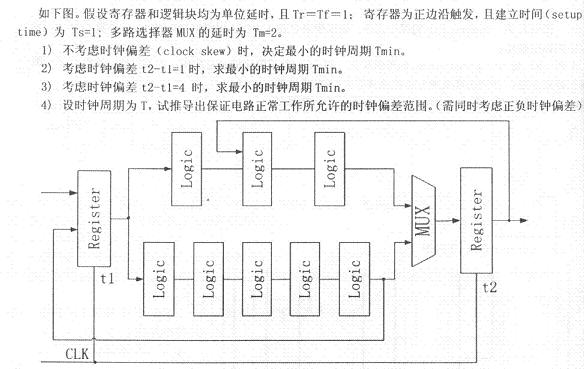

求助一道时序分析题

求解答,谢谢!我算了一下前面三问我算成 9 8 7.

第三个应该为5吧

算第四个的话,还需要寄存器的holdtime吧?

迷茫,不知所云

3# 心海的一滴泪

我没算出来

认为是9,8,6,最后一个时钟偏差指什么不懂?能不能说一下?

第一问应该是9吧,Tmin =Tco+Tlogic+Tsetup=1+5*1+2+1=9

请教2,3个怎么算呢?特别是第三个

第一个是9,第二个是13,Tmin =Tco+Tlogic+Tsetup+t2-t1

第三个不会,有高人指点一下,我记得这道题的前两问在研究生电子设计竞赛中出现过

9# XIAOZZ

后面是减去时钟偏差

求详细解答。新人学习中

支持小编的 9 8 7. 如有错漏请高手指正

1和2不说了。稍稍搜下资料就有了。题目中时钟偏差理解成时钟延迟。

关于第三问。这个图里有三条数据路径。从Q1到D2,Q2到组合逻辑的上支路,组合逻辑的下支路到D1。如果时钟延迟tcd = 4 。则要求时间最长的数据路径就是组合逻辑下支到D1,最小的时钟就是tco+tlogic+tsu = 1+5+1 =7.

第四问。我理解的时钟正负偏差,是指时钟先到达R1为正偏。即t2-t1>0,反之,时钟先到达R2为负偏差。根据上面的数据路径的时间要求。可分别得出。正偏差,tcd>9-T,负偏差,tcd<T-10;由此可见,T至少要大于10才能同时满足两种可能。

没有明白楼上的解释

第三问最长的路径应该是是最上面那条回路,最下面那条路应该只有5吧

我也认为是9,8,6,第三问上面那条路径是最长路

哦看懂了,下面的路径更长,应该是9,8,7

我感觉第一个应该是8,因为采用了流水线结构

求解答。

晕,原来看漏了一条路径

UP下,第四问。

有4条路径,Q1经过上面组合逻辑到D2,延迟为7,Q1经过下面组合逻辑到D2延迟为9,Q1到D1,延迟为7,Q2到D2延迟为6

1):最大的延迟为9,所以T=9

2):计算T时,Q1到D2的两条路径减1,分别为6,8,最大为8,所以T=8

3):计算T时,Q1到D2的两天路径减4,分别为3,5,最大为7,所以T=7

4):Q1到D1和Q2到D2的路径跟偏斜无关,只要分析Q1到D2的2条路径就可以了。我认为正偏斜(t2-t1为正)最大为7,负偏斜最小为9-T。

分析的很好,佩服,只是不解为什么Q2到D2的延时为5,我觉得是6?

我感觉也是6

这个算错了,谢谢指出。

先计算一下data的最大延时,也就是从第一个寄存器的输入端到第二个寄存器输入端之间的延时是5*1+2+1=8. 我们记为Td

(1). 没有时钟偏差的话,最小时钟周期必须大于该延时加上建立时间,也就是Td+Ts=8+1=9,记为Tp

(2). t2-t1=1时,最小时钟周期为数据延时加上建立时间,然后减去该时钟skew,为9-1=8

(3). 原理同(2),为9-4=5

(4). T-9=<x<=9-T

请指点。

嗯,你说的对,我看漏了两条路径。

所以第三问关键路径在Q1-D1上,与skew无关,T不能小于7

第四问skew的范围和保持时间还有关系的吧?熬夜头都晕了。

21 楼的答案是对的 你的

第三问 还需要考虑 Q1~D1的路径, 所以最小T不能小于7, 不然D1 就setup VIO了

第四问 参考21楼答案

嗯,你说的对,我看漏了两条路径。

所以第三问关键路径在Q1-D1上,与skew无关,T不能小于7

第四问skew的范围和保持时间还有关系的吧?熬夜头都晕了。