帮忙看看这道数字逻辑的笔试题

时间:10-02

整理:3721RD

点击:

用filp-flop和logic-gate设计一个1位加法器,输入carryin和current-stage,输出carryout和next-stage.

这个不好做吗?

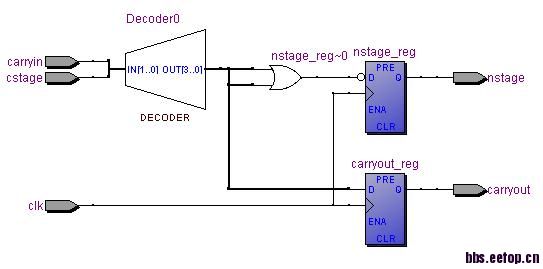

没说寄存器和门的数量或者总类,你看这样行不行:

module add1(clk,carryin,cstage,carryout,nstage);

input carryin;

input cstage;

input clk;

output carryout;

output nstage;

wire carryout;

wire nstage;

reg carryout_reg;

reg nstage_reg;

always@(posedge clk)

begin

case({carryin,cstage})

2'b00: {carryout_reg,nstage_reg} <= 00;

2'b01: {carryout_reg,nstage_reg} <= 01;

2'b10: {carryout_reg,nstage_reg} <= 01;

2'b11: {carryout_reg,nstage_reg} <= 10;

default: {carryout_reg,nstage_reg} <= {carryout_reg,nstage_reg};

endcase

end

assign carryout = carryout_reg;

assign nstage = nstage_reg;

endmodule

附 quartus综合RTL

你这级别不至于问这个问题啊,难道是我想简单了,还是有坑没看到?