电路延时

时间:10-02

整理:3721RD

点击:

由于Xilinx的ISE功能仿真的时候不会考虑延时,所以有时候我的仿真看起来是对的,但是老师说实际上不是对的。

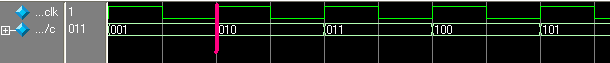

比如如下这个简单的仿真结果:

里面第一个是时钟clk,第二个是数据c.

根据功能仿真,数据c每次都是在时钟上升沿更新数值。而且这个数据接下来是存到memory里面的。memory时钟跟这里的clk相同。

我想问一下,那在第二个时钟上升沿(图中紫色粗线标示)之后,存到memory里面的到底是001还是010呢?

老师说因为电路存在延时(这个当然是一定存在的),所以数据c实际上是在上升沿之后过一段时间才更新数据的,所以第二个时钟沿存到memory的数据是001,而不是010?

请问大侠们,是这样的吗?

比如如下这个简单的仿真结果:

里面第一个是时钟clk,第二个是数据c.

根据功能仿真,数据c每次都是在时钟上升沿更新数值。而且这个数据接下来是存到memory里面的。memory时钟跟这里的clk相同。

我想问一下,那在第二个时钟上升沿(图中紫色粗线标示)之后,存到memory里面的到底是001还是010呢?

老师说因为电路存在延时(这个当然是一定存在的),所以数据c实际上是在上升沿之后过一段时间才更新数据的,所以第二个时钟沿存到memory的数据是001,而不是010?

请问大侠们,是这样的吗?

是这样的。

是001,你用MODELSIM仿真,非阻塞式赋值,上升沿采样的是上一拍的数据。

是。

。

只是想确定一下哈,谢谢各位回答哦,祝元宵节快乐!

呵呵!

第二个时钟存入的数据是 001,而不是010

always(posedge clk )

a_reg<= #1 a;

换这样写,就明白了

学习,学习,呵呵

是001,

看看。。