请教 : 用时钟信号实现复位信号?

时间:10-02

整理:3721RD

点击:

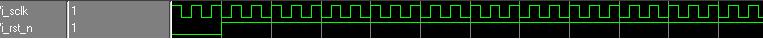

如下图,输入只有时钟信号i_sclk,如果要用时钟信号实现复位信号i_rst_n,能否实现?有什么办法实现?

谢谢!

谢谢!

my way

module myway(i_sclk,i_rst_n );

input i_sclk;

output i_rst_n;

reg [7:0] counter;

always @(posedge i_sclk)

if (counter==128) counter=128;

else counter=counter+1;

assign i_rst_n = (counter==128)?1:0;

endmodule

这样的话counter没有置位信号啊?

initialize the counter in the declaration by using

"reg [7:0] counter=8'b0;"

理论上这样做应该是可以的,但因为你的counter本身没有在一开始复位,所以counter在一开始的状态是不能确定的,所以你的“i_rst_n”信号产生的时间是没有办法确定的!

如果你用FPGA/CPLD,应该是没有问题的,因为初始上电时所用的存储单元都被初始化为0

xuexi