射频集成电路的电源管理

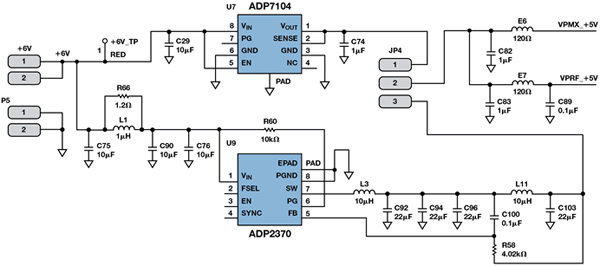

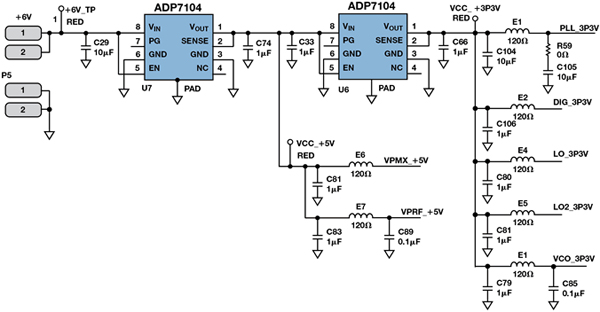

供电轨可以由ADP7104 或ADP2370 驱动。在每个电源引脚上施加额外的去耦和滤波处理。

图9. 5 V 电源设计

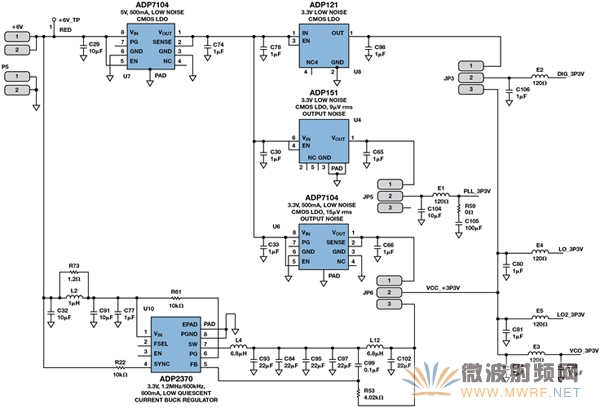

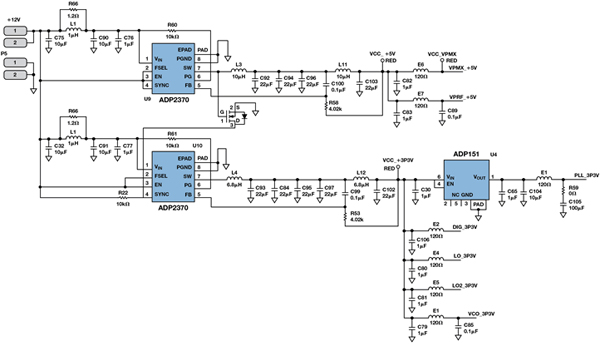

图10 所示为3.3 V 电源设计。源电压仍为6.0 V,但一个额外的LDO 使源电压降至中间电压,然后,源电压进一步降至3.3 V。需要一个额外级以减少功率损耗,因为一个直接降压至3.3 V 的6 V 源电压工作时的最大效率为55%。开关调节器路径不需要中间级,因为其脉冲宽度调制(PWM)架构可降低功率损耗。

3.3 V 设计允许进行更多实验。除了用一个LDO 或开关调节器驱动3.3 V 供电轨以外,VPOS_PLL 供电轨有额外LDO 选项,VPOS_DIG 供电轨有一个可选的隔离式LDO。由于PLL 电源灵敏度最高,因此,我们尝试了三种电源解决方案,每一种都有不同的输出噪声:ADP151 3.3 V 超低噪声CMOS LDO,输出噪声为9 μV;ADP7104 3.3 V 低噪声CMOS LDO,输出噪声为15 μV rms;ADP2370 3.3 V 降压调节器。我们希望确定仍能维持所需相位噪声性能的最高电源噪声。最高性能、最低噪声LDO是不可或缺的吗?

另外还尝试在VPOS_DIG 供电轨上采用ADP121 3.3 V 低噪声CMOS LDO,以确定数字噪声是否会影响性能。受SPI 接口开关影响,数字供电轨的噪声一般高于模拟电源。我们希望确定3.3 V 数字电源是需要自己的LDO,还是可以直接耦合到模拟电源。我们选择ADP121 作为低成本解决方案。

图10. 3.3 V 电源设计

结论和推荐电源设计

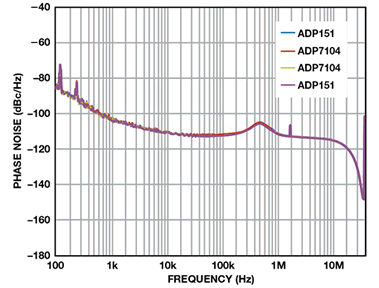

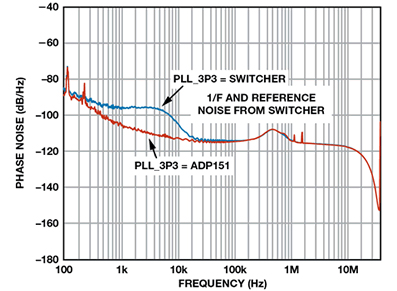

对于VPOS_PLL(最灵敏的供电轨),低成本的ADP151 LDO可以实现与ADP7104 高性能、低噪声LDO 相同的相位噪声,如图11 所示。然而,在采用ADP2370 开关调节器时,性能下降,如图12 所示。噪声波峰由开关调节器导致,在其输出端可见,如图13 所示。因此,VPOS_PLL 最多可以承受15 μV rms的噪声而不造成集成相位噪声性能下降,但不能使用开关调节器来驱动该引脚。使用性能更高、噪声更低的LDO 并未带来好处。

图11. 使用ADP151 和ADP7104 时的集成相位噪声

图12. 使用ADP151 和ADP2370 时的集成相位噪声

在用开关调节器或LDO 驱动剩余供电轨时,可维持良好的相位噪声性能,如图14 所示。5 V 供电轨引脚VMPX 和VPRF 可以相连并用单电源供电。3.3 V 电源引脚VPOS_LO1、VPOS_LO2和VPOS_VCO 也可相连并用单电源供电。VPOS_DIG 不需要独立的LDO,可以连接模拟3.3 V 电源。

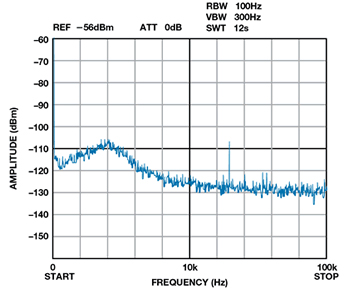

图13. ADP2370 的输出频谱

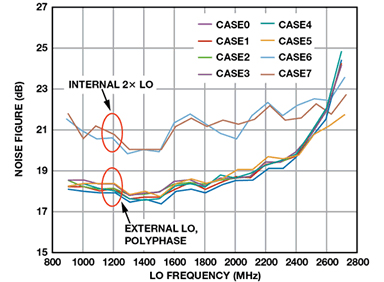

图14. 开关与LDO 噪声系数

推荐电源设计(如图15 所示)采用6 V 源电压,包括ADP7104 5.0 V 和ADP7104 3.3 V LDO。该解决方案只使用了LDO,因为源电压接近所需的电源电压。功效处于可接受水平,因此,无需额外增添滤波元件和开关调节器。

推荐的电源设计(如图16 所示)采用12 V 源电压,包括两个开关调节器和一个LDO。源电压远远大于所需电源电压,因此使用了开关调节器来提高功效。除灵敏的VPOS_PLL 电源以外的所有电源引脚都可用开关调节器供电。ADP7104 或ADP151均可用于VPOS_PLL。

图15. 6 V 源电压的推荐电源设计

图16. 12 V 源电压的推荐电源设计

参考文献

电路笔记CN0147,利用低噪声LDO 调节器为小数N 分频压控振荡器(VCO)供电,以降低相位噪声,ADI 公司,2010 年。

Collins, Ian,集成PLL 和VCO[第2 部分],Radio-Electronics.com,2010 年11 月。

作者:Qui Luu,RF 应用工程师,ADI 公司

- 射频集成电路CAD讨论(04-24)

- Semtech射频集成电路应用(03-05)

- 针对基站和卫星通信的高线性度RF前端解决方案(07-10)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 应用于基站的WiMAX CPE收发器介绍(07-11)

- 基站功率放大器的监控和控制(07-03)