射频集成电路的电源管理

,功耗小于1.5 mW。降低偏置电流会同时降低功耗和性能。增加混频器偏置电流会提高混频器内核的线性度并改善IIP3,但会降低噪声系数,增加功耗。如果噪声系数非常重要,可以降低混频器偏置电流,结果可减少混频器内核中的噪声并降低功耗。类似地,输出端的基带放大器对低阻抗输出负载具有可变电流驱动能力。低输出阻抗负载要求较高的电流驱动,功耗也更高。数据手册列出了一些数据表,其中展示了各种工作模式下的功耗。

测量步骤和结果

供电轨上的噪声耦合会在CW 和IF ±CW 时产生无用噪声。要模拟该噪声耦合情形,在每个电源引脚上施加一个CW 音,测量所形成的混频积相对于输入CW 音的幅度。把该测量值记为电源抑制能力,单位为dB。电源抑制因频率而异,因此,要对30 kHz 至1 GHz 的CW 频率进行扫描,以捕捉到具体的行为数据。目标频带内的电源抑制能力决定了是否需要滤波。PSRR 计算方法如下:

CW PSRR(单位:dB)=输入CW 幅度(dBm) –I/Q 输出端测得的CW 馈通(dBm)

(IF ±CW) PSRR(单位:dB)=输入CW 幅度(dBm) –I/Q 输出端测得的IF ±CW 馈通(dBm)

(IF + CW)(单位:dBm)= (IF –CW) dBm,因为在载波周围调制的CW 音具有相等的幅度。

实验室设置

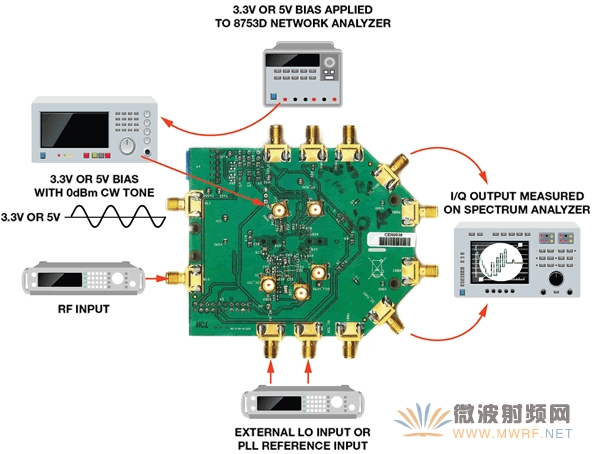

图4 所示为实验室设置。向网络分析仪施加一个3.3 V 或5 V 直流源,以产生失调为3.3 V 或5 V 的扫频连续正弦信号。将该信号施加到RFIC 上的各个供电轨。两个信号发生器提供RF 和LO输入信号。测量频谱分析仪的输出。

图4. ADRF6820 PSRR 测量设置

测量步骤

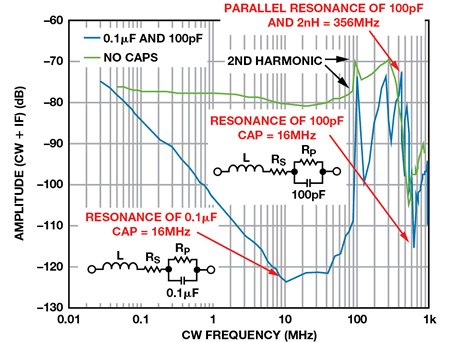

无用混频积的幅度取决于芯片的电源抑制性能,以及评估板上去耦电容的大小和位置。图5 所示为输出端(IF + CW)音的幅度,其中,电源引脚上给定0 dB 的正弦信号。无去耦电容时,无用音的幅度在–70 dBc 和–80 dBc 之间。数据手册建议在板正面器件旁边设置一个100 pF 的电容,在背面设置一个0.1 μF 的电容。从图中可以看到这些外部去耦电容的谐振。16 MHz 处的瞬变是0.1 μF 电容谐振的结果(寄生电感为1 nH)。356 MHz 处的瞬变是100 pF 电容谐振的结果(两个电容的寄生电感均为2 nH)。500 MHz 处的瞬变是100 pF 电容谐振的结果(寄生电感为1nH)。

图5. IF ±CW去耦电容谐振的影响

结果

测量了基带输出端的供电轨上干扰信号(CW)和调制信号(IF ± CW)的幅度。在被测供电轨上引入了噪声,其他电源则保持洁净。图6 所示为在电源引脚上注入0 dB 正弦信号并在30 kHz 至1 GHz 范围内扫频时(IF ±CW)音的幅度。图7 所示为从CW 音到基带输出的馈通。

图6. (IF ±CW)音的PSRR

图7. CW音的PSRR

分析

图中提供了各电源引脚处的电源灵敏度数据,这些数据非常有用。VPOS_PLL 具有最差电源抑制性能,因此,是最灵敏的电源节点。该电源引脚驱动PLL 电路,包括参考输入频率、相位频率检测器和电荷泵。这些灵敏的功能模块决定着LO 信号的精度和相位性能,因此,其上耦合的任何噪声都会直接传播到输出端。

同理,可以认为VCO 电源也是一个非常重要的节点。从图中可以看出,VPOS_VCO 的抑制性能远远优于VPOS_PLL。这是实际驱动VCO 的内置LDO 造成的结果。LDO 将VCO 与外部引脚上的噪声隔离开,同时为其提供固定噪声频谱密度。PLL 电源无LDO,因而是最敏感的供电轨。可见,将其与潜在噪声耦合相隔离对于获得最佳性能至关重要。

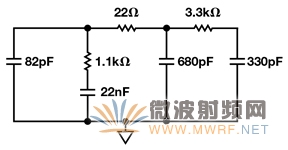

PLL 环路滤波器会衰减高CW 频率,因此,VPOS_PLL 在低频下的灵敏度较差,当频率从30 kHz 扫描至1 GHz 时会缓慢改善。在较高频率下,干扰音的幅度会衰减,注入PLL 的功率水平显著降低。可见,VPOS_PLL 的高频电源抑制性能优于其他电源域。环路滤波器组件是针对20 kHz 配置的,如图8 所示。

供电轨(从灵敏度最高到最低)为:VPOS_PLL、VPOS_LO2、VPOS_VCO、VPOS_LO1、VPOS_DIG、VPMX 和VPRF。

图8. 针对20 kHz 环路带宽配置的PLL 环路滤波器

电源设计

经过前面的讨论,我们对ADRF6820 在各种模式下的最大功耗以及各电源域的灵敏度有了较好的理解,我们利用开关调节器和LDO 来设计电源管理解决方案,以决定两种电源解决方案的可行性。首先,把一个6 V 源调节至5 V 和3.3 V,供ADRF6820供电轨使用。图9 所示为针对VPMX 和VPRF 的5 V 电源设计。ADP7104 CMOS LDO 最多可以提供500 mA 的负载电流。ADP2370 低静态电流降压开关调节器可以在1.2 MHz 或600 kHz 下工作。在开关调节器输出端增加了额外的滤波理,以衰减开关噪声。ADP2370 最高可以提供800 mA 的负载电流。ADRF6820 的5 V

- 射频集成电路CAD讨论(04-24)

- Semtech射频集成电路应用(03-05)

- 针对基站和卫星通信的高线性度RF前端解决方案(07-10)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 应用于基站的WiMAX CPE收发器介绍(07-11)

- 基站功率放大器的监控和控制(07-03)