射频集成电路的电源管理

随着射频集成电路(RFIC)中集成的元件不断增多,噪声耦合源也日益增多,使电源管理变得越来越重要。本文将描述电源噪声可能对RFIC 性能造成的影响。虽然本文的例子是集成锁相环(PLL)和电压控制振荡器(VCO)的ADRF6820 正交解调器,但所得结果也适用于其他高性能RFIC。

电源噪声会在解调器中形成混频积,因而可能导致线性度下降,并对PLL/VCO 中的相位噪声性能造成不利影响。本文将详细描述电源评估方案,同时提供采用低压差调节器(LDO)和开关调节器的推荐电源设计。

凭借双电源和超高RF 集成度,ADRF6820 是适合讨论的一款理想器件。它使用的有源混频内核与ADL5380 正交解调器相似,PLL/VCO 内核与ADRF6720 相同,因此,本文所提供信息也可用于这些器件。另外,电源设计也可用于要求3.3 V 或5.0 V电源、功耗相似的新型设计。

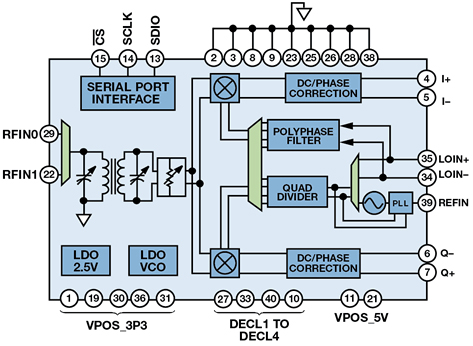

ADRF6820 正交解调器和频率合成器(如图1 所示)非常适合新一代通信系统。该器件功能丰富,包括一个高线性度宽带I/Q 解调器、一个集成小数N 分频PLL 和一个低相位噪声多核VCO。另外集成一个2:1 RF 开关、一个可调谐RF 巴伦、一个可编程RF衰减器和两个LDO。这款高度集成的RFIC 采用6 mm ×6 mmLFCSP 封装。

图1. ADRF6820 简化功能框图

电源灵敏度

受电源噪声影响最大的模块为混频器内核和频率合成器。耦合至混频器内核的噪声会形成无用信号,结果会导致线性度和动态范围下降。这对正交解调器尤其重要,因为低频混频积在目标频带之内。类似地,电源噪声可能导致PLL/VCO 相位噪声性能下降。无用混频产物和相位噪声性能下降是多数混频器和频率合成器的常见问题,但确切的下降幅度取决于芯片的架构和布局。了解这些电源灵敏度有利于设计出更加鲁棒的电源,使性能和效率达到最优。

正交解调器灵敏度

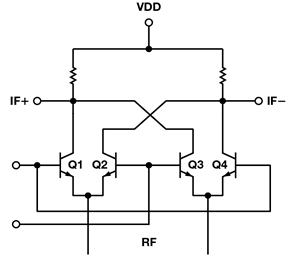

ADRF6820 采用一个双平衡吉尔伯特单元有源混频器内核,如图2 所示。双平衡意味着LO 和RF 端口都采用差分驱动方式。

图2. 吉尔伯特单元双平衡有源混频器

在滤波器抑制高阶谐波以后,所得到的混频器输出为RF 和LO输入的和与差。差项(也称为IF 频率)在目标频带之内,是所需信号。和项在频带之外,要进行滤波处理。

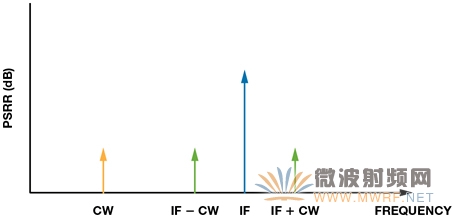

理想情况下,只有所需RF 和LO 信号会输入混频器内核,但很少是这种情况。电源噪声可能耦合到混频器输入中并表现为混频杂散。根据噪声耦合源的不同,混频杂散的相对幅度可能不同。图3 所示为一种示例混频器输出频谱,其中,由于电源噪声的耦合,其与有用信号的混频产物也出现在输出频谱上。在图中,CW 对应于耦合到供电线路的连续波或正弦信号。比如,噪声可能是来自600 kHz 或1.2 MHz 开关调节器的时钟噪声。电源噪声可能导致两个不同的问题;如果噪声耦合到混频器输出,CW 音将没有经过任何频率转换,出现在输出端。如果耦合发生在混频器输入端,则CW 音会调制RF 和LO 信号,并在IF ±CW 产生积。

图3. 电源噪声耦合条件下的示例混频器输出频谱

这些混频积可能接近目标IF 信号,因此,要滤除它们是很困难的,动态范围损失是不可避免的。正交解调器尤其如此,因为它们的基带是复数且以直流为中心。ADRF6820 的解调带宽范围为直流至600 MHz。如果用噪声频率为1.2 MHz 的开关调节器驱动混频器内核,则无用混频积会出现在IF ±1.2 MHz。

频率合成器灵敏度

本文末尾的参考文献针对电源噪声如何影响集成PLL和VCO提供了非常有价值的信息。其原理适用于采用相同架构的其他设计,但不同的设计需要单独进行电源评估。例如,ADRF6820VCO 电源上的集成LDO 比不采用集成LDO 的PLL 电源具有更强的噪声抑制能力。

ADRF6820 电源域和功耗

要设计电源管理解决方案,首先要考察RFIC 的电源域,以确定哪些RF 模块由哪个域驱动、各个域的功耗、影响功耗的工作模式以及各个域的电源抑制性能。利用这些信息,可以收集到RFIC的灵敏度数据。

ADRF6820 的每个主要功能模块都有自己的电源引脚。两个域由5 V 电源供电。VPMX 驱动混频器内核,VPRF 驱动RF 前端和输入开关。其他域由3.3 V 电源供电。VPOS_DIG 驱动一个集成LDO,后者输出2.5 V 以驱动SPI 接口、PLL 的Σ-Δ 调制器和频率合成器的FRAC/INT 分压器。VPOS_PLL 驱动PLL 电路,包括参考输入频率(REFIN)、相位频率检测器(PFD)和电荷泵(CP)。VPOS_LO1 和VPOS_LO2 驱动LO 路径,包括基带放大器和直流偏置基准电压源。VPOS_VCO 驱动另一个集成LDO,后者输出2.8 V 以驱动多核VCO。该LDO 对降低对电源噪声的灵敏度十分重要。

ADRF6820 可配置为多种工作模式。正常工作模式下,采用2850 MHz LO 时

- 射频集成电路CAD讨论(04-24)

- Semtech射频集成电路应用(03-05)

- 针对基站和卫星通信的高线性度RF前端解决方案(07-10)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 应用于基站的WiMAX CPE收发器介绍(07-11)

- 基站功率放大器的监控和控制(07-03)