祖父时代的ADC已成往事:RF采样ADC给系统设计带来诸多好处

此外,由于器件数量更少,系统成本也更低。简化的前端设计可缩短设计时间。

由于现代RF采样ADC集成了非常多的数字处理功能,因此数字处理可以在ADC内部高速进行。如上文所述,这样可以实现高功效和高I/O效率的设计。现在,系统设计人员可以利用其FPGA的未使用JESD204B收发器来服务来自其它RF采样ADC的数据,这些ADC已对数据进行处理(模数转换、滤波和抽取)。这样就可以高效使用FPGA资源,同时提高无线电设计的通道数。

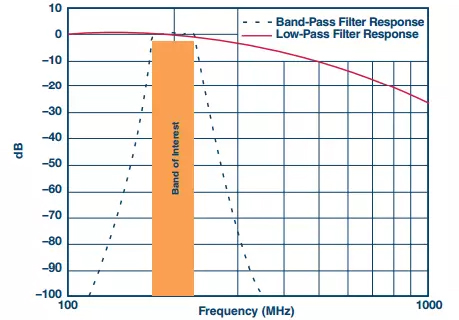

图13. 250 MSPS ADC和1 GSPS ADC的AAF比较

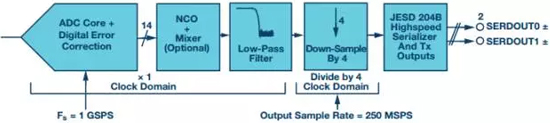

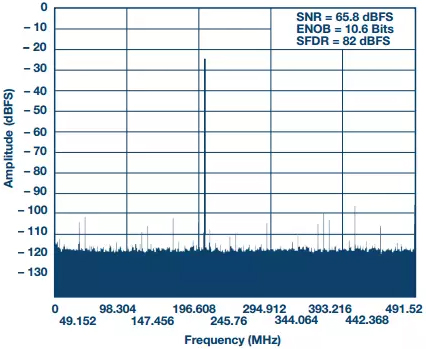

利用DDC,ADC可以用作数字混频器来调谐至设计需要的任何中频。本例同样使用上述频率规划。采用¼抽取选项和实数混频来演示ADC性能,如图14所示。

图14. RF采样速率为1 GSPS,DDC设置为1/4抽取

在正常或全带宽模式下,AD9680的SNR约为66 dBFS至67 dBFS。当DDC处于工作状态且抽取比为¼时,还可以获得6 dB的额外处理增益[3]。这样可以确保动态范围性能保持不变。由于RF采样ADC以4倍原始采样速率采样,因此谐波会扩展(如图10所示)。RF采样ADC中的DDC确保抽取滤波器以数字方式衰减干扰信号。然而,属于目标频段内的谐波(更高阶或其它)仍会显示,因为DDC允许其通过。引起它的原因可以是放大器伪像或低通滤波器没有足够的衰减能力。低通滤波器可以根据系统要求重新设计,以满足其它杂散性能要求。

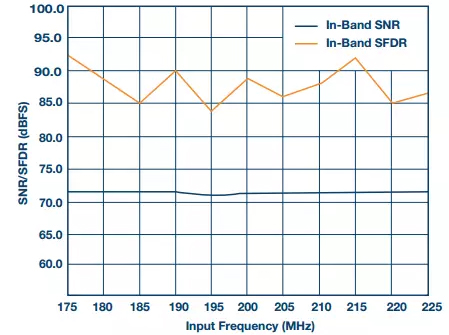

图15显示了1GSPS ADC的SNR/SFDR与输入频率的关系。数据清楚地表明,DDC的使用使得SNR提高6 dB (原因是处理增益),SFDR也得到改善。在全带宽模式下运行时,SFDR通常受二次或三次谐波限制,而在DDC模式(¼抽取)下,限制因素为最差其它谐波。

图15. 图12所示14位1 GSPS ADC设计的SNR/SFDR与频率的关系

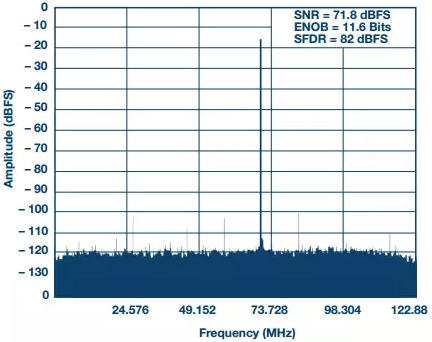

抽取输出的FFT如图16所示。使用DDC时,必须采取措施确保目标频段得到正确处理。本例中,NCO调谐至200 MHz,使得目标频段落在抽取奈奎斯特区的中央。DDC可以方便地消除频谱中不需要的频率。因此,FPGA的处理开销更低。

图16. 1/4抽取时1 GSPS ADC的205 MHz FFT;NCO调谐至200 MHz

作为对比,图17显示了AD9680在正常(全带宽)工作模式下的FFT。

图17. 全带宽模式下1 GSPS ADC的205 MHz FFT

通过这些图形可知,DDC除了能改善带内噪声性能之外,还能提供无干扰谐波的清洁频谱。由于DDC对数据进行滤波和抽取(至250 MSPS),因此还会降低输出通道速率,这使得JESD204B串行接口具有更灵活的选项。系统设计人员可以选择高通道速率(较昂贵)、低I/O数FPGA或低通道速率(较便宜)、高I/O数FPGA。

结论

RF采样ADC为系统设计提供了独特的优势,而在几年前,这是无法实现的。业界期望加速基础设施的设计和实现,以便应对更高的带宽需求。设计时间和预算不断缩减,对可扩展、可重新配置、更多由软件驱动的架构的需求催生出新的设计范式。更高带宽的需求伴随着更高容量的需求。这就给FPGA I/O带来了更大的压力,而RF采样ADC可以利用内部DDC予以化解。

- 针对基站和卫星通信的高线性度RF前端解决方案(07-10)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 应用于基站的WiMAX CPE收发器介绍(07-11)

- 基站功率放大器的监控和控制(07-03)

- ADI RF信号源解决方案(10-20)

- 用于可靠的电容传感器接口的模拟前端IC测量方法(07-30)