祖父时代的ADC已成往事:RF采样ADC给系统设计带来诸多好处

外部器件,缩短设计时间。

通信接收机设计更加灵活

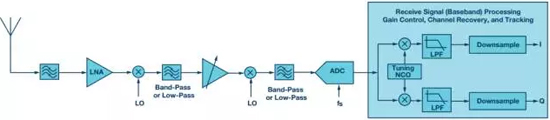

一个非常常见的ADC使用案例是通信接收机系统设计。图3所示为较早一代无线电接收机的功能框图。

图3. 用于蜂窝无线电的宽带数字接收机

GSM无线电接收机的一般规格要求ADC的噪声频谱密度(NSD)至少为153 dBFS/Hz或更佳。众所周知,NSD与ADC的SNR存在如下关系:

NSD = SNR + 10 log10 (fs ÷ 2)

其中:

SNR的单位为dBFS

fs = ADC采样速率

常规软件无线电设计

在宽带无线电应用中,对高达50 MHz的频段同时进行采样和转换并不是罕见的事。为了正确地对50 MHz频段进行数字化,ADC将需要至少5倍的采样带宽,即至少约250 MHz。将这些数值代入上式,ADC达到–153 dBFS/Hz NSD要求所需的SNR约为72 dBFS。

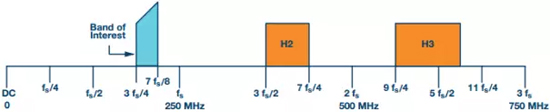

图4显示了利用250 MSPS ADC对50 MHz频段有效采样所采用的频率规划。该图还显示了二次和三次谐波频段的位置。

图4. 采用250 MSPS ADC的50 MHz宽带无线电的频率规划

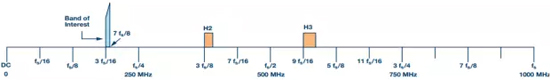

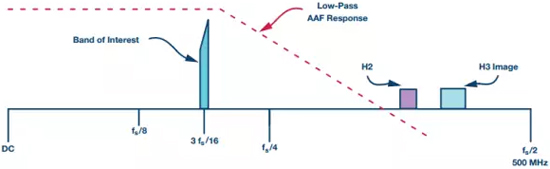

ADC采样的频率都会落在ADC的第一奈奎斯特(DC –125 MHz)频段。这种现象称为混叠,因此这些频率包括目标频段、折回或混叠到第一奈奎斯特频段的二次和三次谐波,如图5所示,说明如下:

图5. 显示在第一奈奎斯特区中的可用频段,含二次和三次谐波

除NSD规格外,GSM、LTE和LTE-A等蜂窝通信标准还对SFDR (无杂散动态范围)有其它严格要求。这给前端设计带来了很大压力;对目标频段中的信号进行采样时,前端能够衰减干扰信号。

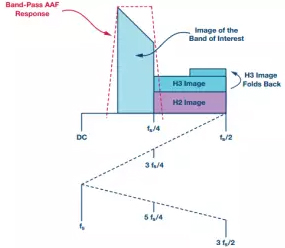

注意,常规无线电前端设计的SFDR规格,即抗混叠滤波器要求很难达到。满足SFDR要求的最佳抗混叠滤波器(AAF)解决方案是采用带通滤波器。通常,此类带通滤波器为五阶或更高阶。一款可以满足此类应用的SNR (或NSD)和SFDR要求的合适ADC是16位250 MSPS模数转换器AD9467,采用AD9467的蜂窝无线电应用前端设计将类似图6所示。

图6. 包括放大器、抗混叠滤波器和250 MSPS ADC的前端设计

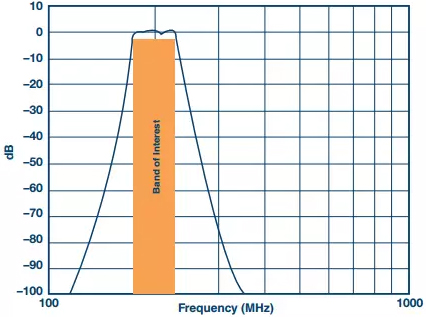

满足SFDR要求的AAF的频率响应如图7所示。此系统的实现不是不可能,但存在很多设计难题。带通滤波器涉及到大量器件,是最难实现的滤波器之一。器件选择非常重要,任何不匹配都会导致ADC输出中出现不需要的杂散(SFDR)。除了非常复杂以外,任何阻抗不匹配都会影响滤波器的增益平坦度。为了优化该滤波器设计以满足带通平坦度和阻带抑制要求,需要做相当多的设计工作。

图7. 图6所示前端的带通响应

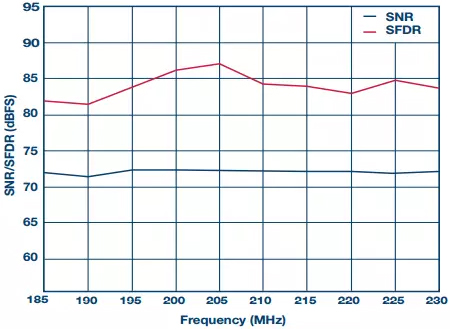

虽然这种无线电设计的前端实现很复杂,但它确实有效,如图8中的SNR/SFDR性能与频率的关系曲线所示。

图8. 图6所示16位250 MSPS ADC设计的SNR/SFDR与频率的关系

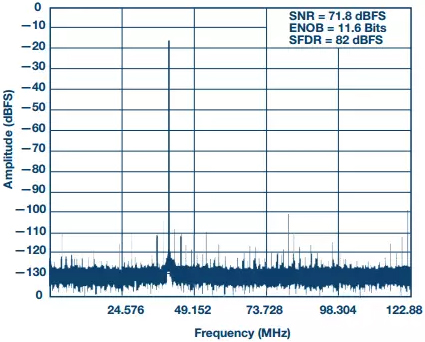

205 MHz时的FFT如图9所示。然而,系统实现因为下列原因而变得复杂:X 滤波器设计。X FPGA必须提供专用I/O端口来捕捉LVDS数据(16对),这会使PCB设计复杂化。X FPGA还需要留出一些处理能力来进行数字信号处理。

图9. 图6所示16位250 MSPS ADC设计在205 MHz时的FFT

RF采样ADC简化并加速设计

RF采样ADC方法采用过采样技术,然后抽取数据以改善动态范围。深亚微米CMOS技术提供的速度优势与高数字集成度能力相结合,开创了RF采样ADC的新纪元,它现在能执行大量重要处理,而不只是简单的模数转换。这些ADC拥有更多的数字电路,支持高速信号处理。

对系统设计人员来说,这意味着实现起来很简单,并可获得其它灵活性,而这在以前一直属于ASIC/FPGA领域。上面的无线电设计示例也可以利用RF采样ADC实现。AD9680 (14位、1GSPS JESD204B、双通道ADC)是一款新型RF采样ADC,而且还有其它数字处理能力。此ADC在全速率(1 GSPS)时的NSD约为67dBFS。现在还不用担心SNR,因为稍后就会知道。目标频段与之前相同,但关于RF采样ADC奈奎斯特区的频率规划要简单得多,如图10所示。这是因为该ADC的采样频率(1 GHz)是上述例子(250 MHz)的4倍。

图10. 采用1 GSPS ADC的50 MHz宽带无线电的频率规划

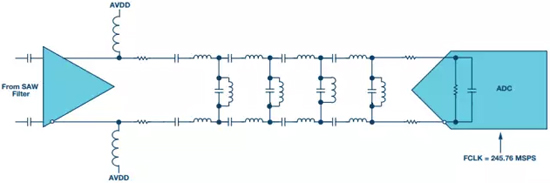

从频率规划可知,它实现起来要比图4所示简单得多。AAF要求也有所降低,如图11所示。这种方法的思想是使用简单的模拟前端设计,而把数字处理模块留在RF采样ADC内以执行繁重的信号处理。

图11. 1 GSPS ADC的AAF移植

过采样的好处是将该频率规划扩展到整个奈奎斯特区,即比250 MSPS奈奎斯特区大4倍的区域。这样就大大降低了滤波要求,一个简单的三阶低通滤波器就足够,而无需250 MSPS ADC方案所用的带通滤波器。采用RF采样ADC的简化AAF实现方案如图12所示。

图12. 包括放大器、抗混叠滤波器和1 GSPS ADC的前端设计

图13所示为低通滤波器响应性能。同时显示了带通滤波器以作比较。低通滤波器的带通平坦度更佳,而且就器件不匹配而言更容易管理。其阻抗匹配也更容易实现。

- 针对基站和卫星通信的高线性度RF前端解决方案(07-10)

- 对比ADI两代TD-SCDMA射频IC得到的启示(05-02)

- 应用于基站的WiMAX CPE收发器介绍(07-11)

- 基站功率放大器的监控和控制(07-03)

- ADI RF信号源解决方案(10-20)

- 用于可靠的电容传感器接口的模拟前端IC测量方法(07-30)