后摩尔定律时代,半导体厂商应该怎么做?

目前在市场上只有来自荷兰的设备业者ASML能供应EUV微影系统,是该公司投入了三十年时间与庞大研发成本的成果,而该公司甚至获得了英特尔、台积电与三星(Samsung)等半导体大厂的联合投资,这些股东们的首要目标就是加速EUV技术的实现。 ASML发言人表示:"我们预期EUV微影将在个位数奈米制程节点被应用于内存中的两个或更多层;而在最先进的逻辑制程节点(7或5奈米),则被应用于6~9层。 "

ASML的第一代(采用0.33NA光学镜片、实现约13奈米的线宽) EUV微影设备NXE:3400B将在今年正式出货,预期吞吐量可达每小时125片晶圆、微影迭对(overlays)误差容许度在3奈米以内;该公司表示已有4家逻辑芯片制造商、2家内存芯片制造商表示将在2018年左右采用第一代EUV系统进行量产。

图3:ASML的EUV微影设备发展蓝图 (来源:ASML)

采用今日的浸润式微影设备需要以多重光罩才能实现的电路图形,若采用0.33NA的EUV系统预期只需要单一光罩步骤就可完成;不过半导体制程若再继续往更细微节点迈进,就算采用EUV设备也可能需要多重图形步骤。

为此ASML于去年11月就宣布以11亿美元收购光学大厂蔡司(Carl Zeiss)的24.9%股份,双方将连手研发数值孔径(numerical aperture,NA)高于0.5的版本,不过此第二代EUV微影要到2024年以后才会量产,将能实现约8奈米的线宽,预期产量为每小时185片晶圆产量、 迭对误差容许度小于2奈米。

ASML技术长Martin van den Brink在发表上述合作案时的新闻声明中指出,新一代(0.5NA)系统将"可在次3奈米节点为芯片制造商避免复杂且昂贵的0.3NA系统多重图形步骤,以单次曝光支持高生产力,并可降低单位成本。 "

不过市场研究机构VLSI Research总裁Risto Puhakka表示,产业界人士仍广泛预期,在第二代EUV系统于2024年左右问世以前,恐怕还是得使用第一代0.33NA微影系统进行多重图形。 "只是需要几重图形、以及会需要多久时间? "他也指出,以往ASML不曾直接投资供应链上的任何厂商,而且是以大手笔收购高比例股份,显见要打造更新一代EUV系统是高风险任务,而且ASML势在必得。

看来如果一切顺利,2018年就能看到第一批采用EUV微影设备量产的先进制程节点IC;但机台尺寸几乎等同一间小房间的EUV,一台要价超过1亿美元(至少31亿台币),这意味着除非是财力够雄厚的半导体厂商,很难负担此尖端技术的投资。

而千呼万唤始出来的EUV微影设备就算真的在2018年之后顺利上线量产,在终端应用市场如PC、智能型手机等成长停滞、缺乏大量需求的趋势下,采用该设备之先进制程初期成本与风险势必仍然偏高,IC业者如果想只靠EUV来维持摩尔定律"制程越微缩、晶体管单位成本越低"的理论,恐怕并不容易。

所以,除了"传统"的半导体制程微缩,IC厂商们还有什么别的方法能维持利润?

其他的技术选项

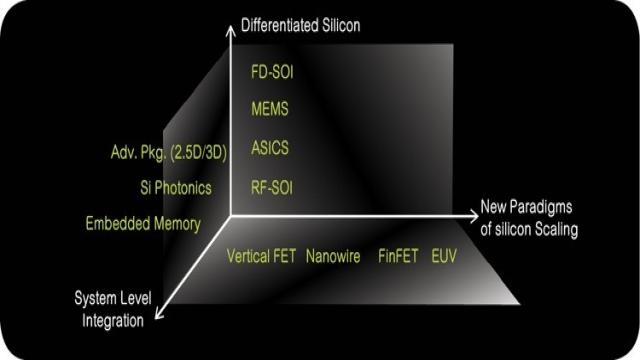

也出席了今年1月美国ISS 的Globalfoundries技术长Patton在专题演说中表示:"摩尔定律将终结只是一个看法,我们总是能找出如何推动事情演进的方法;"他认为,芯片业者现在必须要在制程以及封装技术方面寻求不同方向的创新(图4),"整个产业环境跟我入行的时候已经完全不一样了。 "

图4:除了追随摩尔定律,Globalfoundries技术长Gary Patton认为IC业者应该寻求不同方向的制程与封装技术创新

在半导体产业界拥有超过三十年经验的Patton,在先前向台湾本地媒体简报Globalfoundries技术策略时表示,今日市场上有各种各样新崛起的电子装置与终端应用,例如行动运算、普适运算(pervasive computing,例如无所不在的连网智能装置)以及人工智能(AI)、虚拟/扩增实境(AR/VR)。.. 等等,单一技术并不一定适合所有应用的需求。

Patton表示,人工智能、云端运算、高速通讯等应用,目前最尖端的3D晶体管FinFET制程是理想选择,目前该技术进入14奈米节点量产、已经成熟而且对高阶应用有价值;至于对运算性能要求较低、也以较低功率运作的各种嵌入式装置,例如物联网设备,其实就不一定要用到最尖端的FinFET制程,否则并不符合成本效益。

GlobalFoundries提供的其他技术选项是全空乏绝缘上覆硅(Fully depleted silicon-on-insulator,FD-SOI)制程;Patton指出,该公司准备在2017年量产的22奈米FD-SOI制程,在成本上与成熟的28奈米平面晶体管制程相当,但能达到类似FinFET制程的性能,而且功耗更低、 封装尺寸更小,也更适合与RF组件的整合。

在封装技术方面,Patton表示在过去一年来,Globalfoundries看到2.5D与3D芯片堆栈的客户需求有大幅成长

- 后摩尔定律时代的PCB发展趋势分析(06-20)

- 跨界联盟联合汽车厂商与半导体厂商共商5G车用方案(09-30)

- 5G将至,哪个半导体厂商能够脱颖而出?(10-09)

- 5G,能为半导体厂商带来什么?(11-10)

- 摩尔定律已不再能降低芯片价格(12-19)

- 摩尔定律消退后 计算机行业将如何发展?(03-28)