基于DDS+PLL技术的频率合成器的设计

引言

频率合成技术是近代电子系统和装备的重要组成部分,在无线电技术和电子系统的各个领域均得到了广泛的应用。频率合成即把若干个稳定的标准频率经过"加、减、乘、除"四则运算,产生一系列新的具有同样稳定度和准确度的频率的过程。目前的频率合成的基本方法包括:直接频率合成(DS)、间接频率合成(IS)以及直接数字频率合成技术(DDS)。直接数字频率合成是将数字处理的技术与方法引入信号合成领域的一项新技术,它从相位的概念出发进行频率合成,通过DSP或FPCA对DDS输出波形的频率、幅度、相位实行精确的控制。本文采用DDS与PLL相结合的方式,并在FPGA的控制下,产生高频率、高分辨率以及短频率转换时间的信号波形。

1 方案拟定

1.1 DDS基本原理

典型的DDS由四部分构成,分别为:N位相位累加器、波形存储器、数/模转换器和低通滤波器。其原理为:由一个高稳定的晶体振荡器提供参考时钟频率,用于DDS中各部分同步工作。将频率控制字K送入相位累加器的输入端,相位累加器在参考时钟的作用下,按照频率控制字K对频率进行线性相位取样;对波形存储器寻址,使相位码转换为相应的波形幅度码;再经过数模转换器得到模拟的阶梯波;最后经低通滤波器得到所需频率的波形。

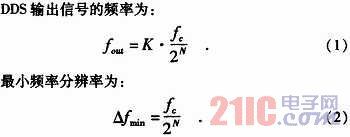

设fc为参考时钟频率,频率控制字为K,N是相位累加器的字长,则

1.2 DDS+PLL技术的优势

DDS具有极高的频率分辨率、近似实时的频率转换时间、任意波形的输出和便于程控等特点,但其合成频率较低,则限制了它的应用范围。而PLL具有的频带宽、工作频率高、频谱纯等优点正好可以弥补DDS的不足之处。两者的结合,不仅简化了电路、减少了硬件的使用量,同时还降低了功耗。

DDS的输出信号作为PLL的参考频率源,使得输出具有较高的频率分辨率,同时PLL作为一个可编程的倍频器,可将DDS产生的频率倍频到所需要的频率范围。当锁相环锁定的时候,频率合成器的输出频率为:

其中fc为DDS的时钟频率,K为DDS的频率控制字,N为DDS的相位累加器字长。

通过(5)式可知,基于DDS与PLL技术的频率合成器中,DDS可以输出一个低频信号,通过PLL的倍频合成后达到高频信号的输出范围,与此同时系统输出的信号也能有较高的频率分辨率。

2 频率合成器实现

2.1 方案设计

本设计采用DDS激励PLL的方式实现频率从低频倍频至高频。其中,DDS芯片选取AD公司生产的AD9852,PLL芯片选取AD公司生产的ADF43 60-7芯片。外部通过FPGA对DDS实现控制工作,其无限次反复编程的功能保证了DDS波形产生的持续时间大于锁相环的捕捉时间,从而产生所需的输出频率。

AD9852的DDS系统有双48 bit可编程频率寄存器,在数据进入正弦查表之前截断,只对高17位进行正弦查表,最后再由内部集成的12 bit DAC产生模拟信号输出。它的内核部分最高可以工作在300 MHz,时钟信号可直接或者间接通过可编程时钟乘法器(4×—20×)输入内核,通过间接的方式降低外部时钟的频率,而内核的时钟频率保持不变。本设计基于间接时钟输入的方式,以30 MHz外部有源晶体振荡器提供稳定的时钟频率输入,通过内部可编程时钟乘法器进行4倍频,保证了工作频率为120 MHz。

锁相环输出部分采用的是ADF4360-7芯片,其输出频率从350 MH~1 800 MHz,且内部集成VCO,可由外部电感值的改变选择不同的工作频段。主要由低噪声数字鉴相器、可编程分频器R(14 bit)、可编程A(5 bit)、B(13 bit)寄存器和一个双模分频器(P/P+1分别为8/9,16/17)构成。其合成的分频比满足:N=B×P+A,其中,B≥A且N≥(P2-P)。

2.2 方案实施

本设计中AD9852采用串行数据输入模式,在该模式下需要对芯片CS、IO RESET、SDO、SDIO、OSK、I/O UD CLK以及SCLK进行控制信号输入设置。AD9852工作电压为3.3 V,通过将5 V稳压源的输入电压转为3.3 V控制电压,以保证芯片的正常工作,从而防止过高的控制信号输入烧坏DDS芯片。

按照串行控制方式将FPGA与DDS外围电路布置完整,然后通过FPGA进行DDS芯片的初始化。初始化过程中的关键在于,一是对地址与数据的寄存器进行设置,写入各寄存器工作方式所需的控制码;二是初始化串行模式;三是通过串行模式,将FPGA产生的控制码写入到DDS相应的控制寄存器中。

在写地址与数据的寄存器中,主要需要写入的寄存器为frequency tuning word、Delta frequency reaster、update clockrate regis-ter、Ramp rate clock reaster、control register这五个寄存器。其中频率控制字K可按照公式(6)进行计算。

设计中所需产生输出频率为10 MHz,其中N=48,fc=180 MHz,通过公式计算出K=15637498706140转换为十六进制为E38E38E38DC,所以对AD9852的频率控制字寄存器的赋值可表示为data_o<=48’hOE38E38E38DC。

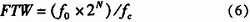

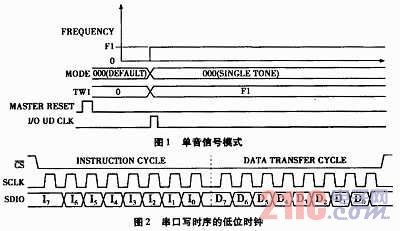

在DDS芯片写数据的过程中,首先,向dds_mareset输入正脉冲信号将DDS复位,然后地址位和数据位分别写入DDS相对应的管脚。在dds_ cs下降沿的触发下,dds_sdio写入可持续八个dds_sclk周期s_wr_inst,该instruction byte决定了接下来的对传输数据读操作或者写操作。经过多次写脉冲操作之后,控制寄存器与频率控制字均写入DDS芯片中,在dds_ioreset的上升沿作用下输出所需频率。如图1、图2所示。

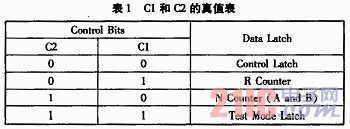

ADF4360-7采用3线串行接口,其数字部分包括24位移位寄存器、14位R计数器以及由5位A计数器和13位B计数器构成的18位N计数器。数据在每个时钟上升沿的作用下移入24位移位寄存器中,并在LE上升沿的触发下,从移位寄存器传输至锁存器中。该锁存器状态由C2和C1两个控制位决定,如表1所示。

本设计中,AD9852采用SINGLE TONE模式,为ADF4360-7提供稳定的10 MHz频率作为其参考信号源。ADF4360-7采用的分频比尺为10,VCO输出频率可通过公式(7)计算得出:

其中,P为前置预置分频比,本设计中取P值为8。

2.3 测试结果

根据上文中对各参考部分的设计,通过使用示波器对各频率点分别进行测试。其中,经R分频后得到1 MHz的鉴相频率,N计数器可用公式N=B×P+A进行计算,即设计寄存器A、B的参数,就可改变N的取值。

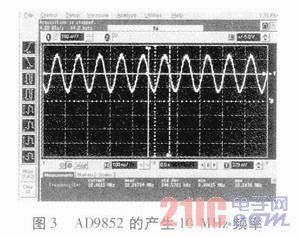

在测试的过程中,首先测试AD9852当前所产生的频率,该频率作为锁相环的信号源,提供的是稳定的10 MHz信号,测试结果如图3所示。理论输出值为10 MHz,实际的输出值为10.46 MHz,考虑到测量误差等因素,该输出频率符合设计的要求。

DDS的输出频率经锁相环倍频后,从低频信号倍频至高频信号,通过对750 MHz、800 MHz、850 MHz、960 MHz几个频率点分别进行测试。测试结果如图4、图5、图6、图7所示。测试结果均是以850 MHz做为中心频率,每格为100 MHz作为标准,其测试结果分别为752.83MHz,798.85 MHz,851.84 MHz,960.25 MHz,均在允许的误差范围内。

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 直接数字频率合成器的实现设计方案(03-01)

- 基于DDS芯片和集成锁相芯片构成的宽频合成器设计(05-25)

- 基于单片机与FPGA的直接频率数字合成器的设计方案(02-23)

- 一种基于LMX2485E芯片的调制倍频电路(02-20)