基于DDS芯片和集成锁相芯片构成的宽频合成器设计

摘 要:结合数字式频率合成器(DDs)和集成锁相环(PLL)各自的优点,研制并设计了以DDS芯片AD9954和集成锁相芯片ADF4113构成的高分辨率、低杂散、宽频段频率合成器,并对该频率合成器进行了分析和仿真,从仿真和测试结果看,该频率合成器达到了设计目标。该频率合成器的输出频率范围为594~999 MHz,频率步进为5 Hz,相位噪声为-91 dBc/

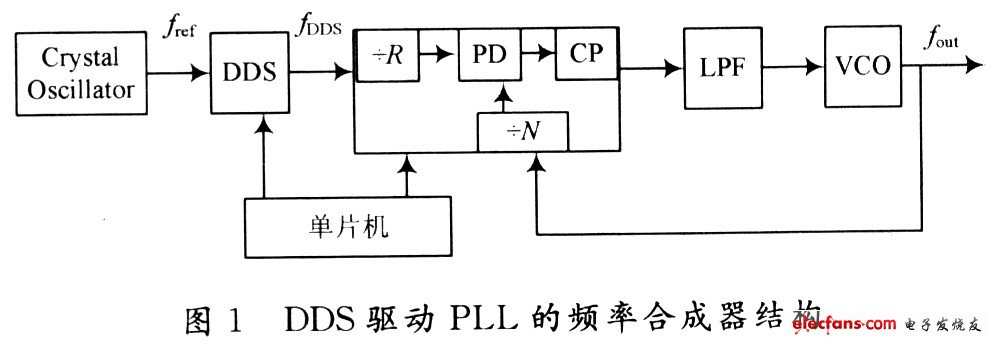

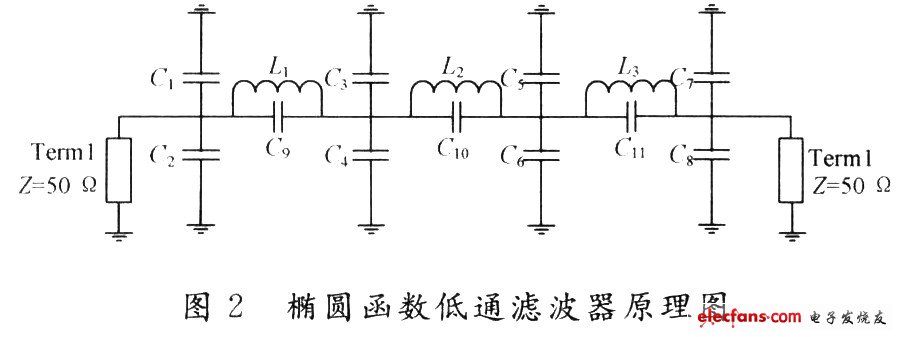

DDS的参考信号由晶振产生,其频率为fref。DDS输出的信号频率为fDDS,频率值由频率控制字(FTW)控制。锁相环(PLL)的参考信号由DDS的输出信号驱动。VCO的输出频率由PLL芯片的电荷泵(CP)输出,并通过低通滤波器(LPF)后控制。频率合成器的输出信号为VCO的输出信号。该频率合成器通过单片机提供控制信号,以改变DDS中FTW和PLL的分频比。

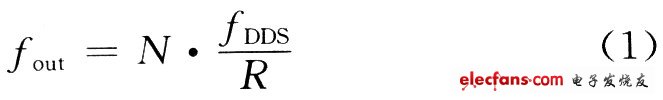

VCO输出信号频率与DDS输出信号频率间的关系为:

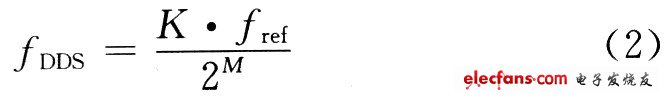

而DDS的输出频率由频率控制字K控制,且有:

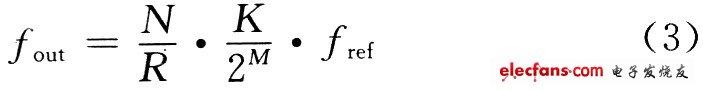

式中:M是DDS的相位累加器的位数;fref是DDS的内部时钟。这样,式(1)可以写成:

在图1所示的结构中,由于DDS模块具有较高的频率分辨率,所以从式(3)可以看出,理论上输出信号具有比传统结构更高的频率分辨率。设计中晶振频率为400 MHz,PLL分频比为27。由式(3)计算可知,该频率源可以实现5 Hz的频率分辨率。其中DDS的输出频率为22~37 MHz,所以系统输出频率范围为594~999 MHz,达到了设计要求。

l.2 电路实现

对于DDS模块,采用了AD9954芯片产生低频参考信号。AD9954是ADI公司最新的AgiIeRF合成器,具有32位的频率控制字。在400 MHz的时钟频率下,输出频率分辨率可以达到约4.7×10-5Hz,具有14位可编程移相单元。芯片采用了先进的:DDS技术,内部集成14位的高性能DAC。该DAC具备优秀的动态性能,相位噪声优于-120 dBc/

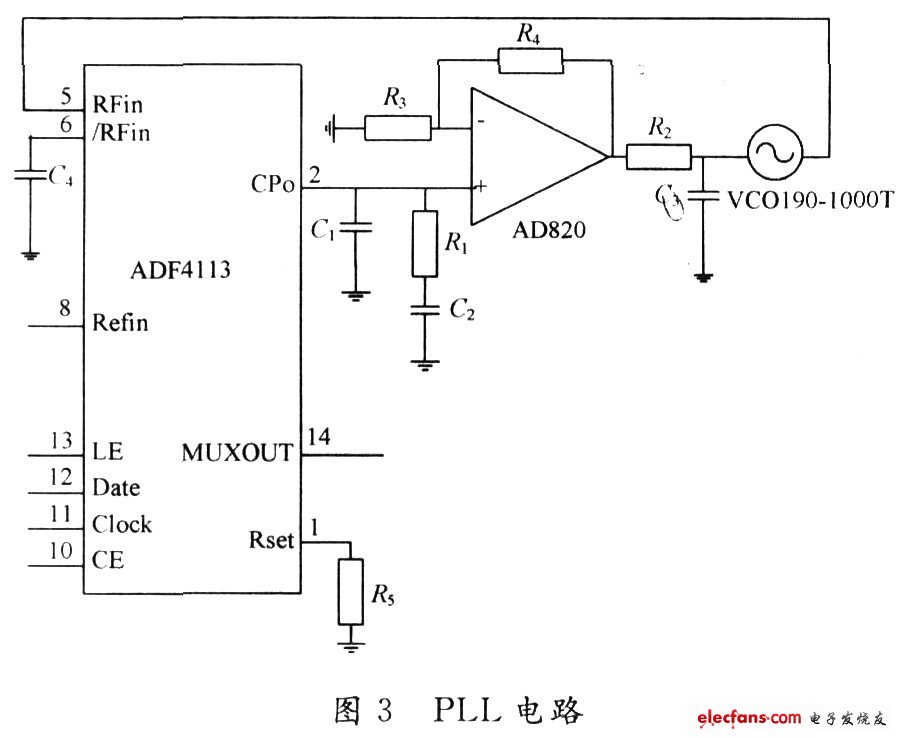

PLL模块在该设计结构中尤为重要。在此采用ADF4113锁相环芯片。ADI公司研制的数字锁相频率合成器ADF4113,最高工作频率可达4 GHz,主要应用于无线射频领域,用以构成数字锁相环,锁定某一频率。该电路内部资源主要包括可编程的模分频器:8/9,16/17,3z/33,64/65;可编程的14位参考频率分频器;可编程的射频信号分频器;3线串行总线接口;模拟和数字的锁定状态检测功能。该芯片的最高鉴相频率达到55 MHz,芯片的底噪为-171 dBc/

2 电路分析与仿真

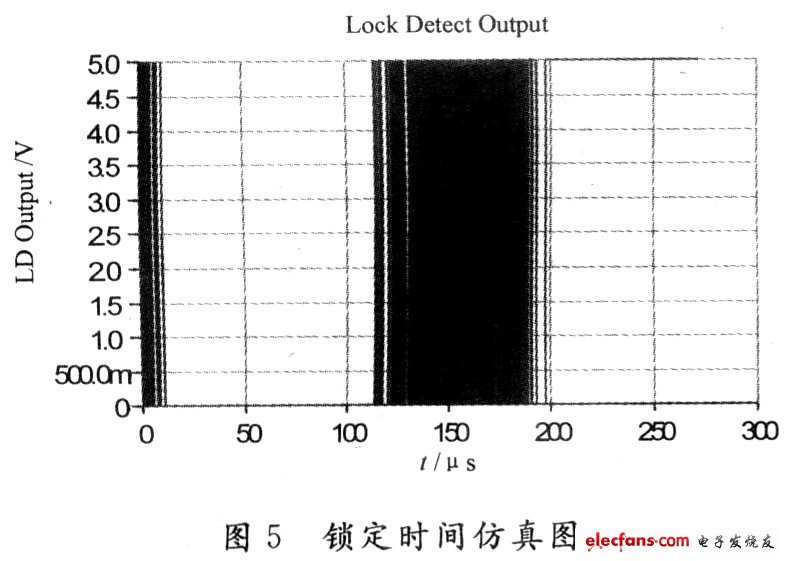

为了分析和评估提出的频率综合器性能,采用ADISimPLL软件对该方案的相位噪声模拟仿真。仿真结果如图4,图5所示。这里给出频率为810 MHz,环路带宽为120 kHz的相位噪声仿真图形以及锁定时间图形,从图中可以看出,该方案满足了设计目标的要求。

3 实验及测量结果

为了检验文中给出的频率综合器性能,使用Agi-lent E4401B对扫频源的相位噪声、杂散进行测量,测量结果如图6~图8所示。594~999 MHz包含了很多频点,测试时选择了一系列较有代表性的点进行测量,限于篇幅,这里给出810 MHz频点相位噪声和杂散的测量结果。由图可见,相噪为-92 dBc/

4 结语

介绍了一种采用DDS激励PLL的频率合成器,有效地克服了宽带系统中DDS输出频率较低和PLL频率分辨率低的缺点。取长补短实现频率合成,实现了单一技术难以达到的效果。

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 直接数字频率合成器的实现设计方案(03-01)

- 基于单片机与FPGA的直接频率数字合成器的设计方案(02-23)