基于锁相环的Chirp超宽带信号源的设计与实现

引言

Chirp超宽带信号是一种瞬时频率随着时间线性变化、同时又符合美国联邦通信委员会(FCC)对超宽带相对带宽定义的信号,由于其具有抗干扰能力强、发射功率低、多径分辨能力强、对频偏不敏感等优点,现已在无线通信、雷达、精确定位等众多领域引起了广泛研究。为了获得高调频线性度、高稳定性的Chirp超宽带信号,国内外学者研究出多种产生Chirp超宽带信号的方案,常见的有模拟法和数字法。模拟法可分为有源法和无源法,有源法是用模拟信号直接控制压控振荡器(VCO),使压控振荡器输出Chirp超宽带信号,这种方法易实现,并且在宽频带内能获得满意的线性特性,但是载频稳定性差;无源法一般是使用声表面波(SAW)器件来产生Chirp超宽带信号,该方法的优点是产生的Chirp超宽带信号频率和带宽可以达到较高,但是其使用灵活性不够,SAW器件一经生产定型,扫频速率、扫频起始频率和扫频时间等参数就确定了,无法更改,并且成本高。数字法是采用直接数字频率合成技术(DDS)来产生Chirp超宽带信号,该方法的优点是产生的Chirp超宽带信号频率分辨率高、频率转换时间短,但是存在相位噪声大、频谱杂散大等缺点。

本文在直接模拟法的基础上,提出了一种基于锁相环的模拟法来产生Chirp超宽带信号设计方案,并用相应的硬件电路实现了该设计方案。该方法能够产生高调频线性度、高稳定性的Chirp超宽带信号,克服了传统的模拟法载频稳定性差的缺点,并且具有低复杂性、低成本,灵活性强以及易于实现等优点。

1 基于锁相环的Chirp超宽带信号源的设计原理

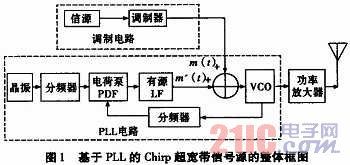

基于锁相环法的Chirp超宽带信号源的设计方案如图1所示,从图中可以看出该设计方案主要由调制电路和锁相环(PLL)电路两大部分构成。调制电路主要由信源、调制器两部分组成,其作用是产生一个速率和幅度可调的线性模拟信号,通过改变该模拟信号的速率和幅度可灵活控制Chirp超宽带信号中的参数。锁相环电路是该方案的核心部分,主要由鉴相器PD、环路滤波器LF和压控振荡器(VCO)三部分组成,其作用是完成Chirp超宽带信号的产生。

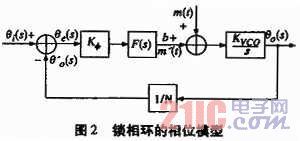

为了分析锁相环产生Chirp超宽带信号的原理,建立锁相环的相位模型如图2所示。调制信号m(t)由LF与VCO之间注入环路中,图中θi(s)为基准输入信号的相位,θo(s)为VCO输出信号的相位,θ'o(s)为输出信号经分频器后反馈到鉴相器的相位,θe(s)为鉴相器输出相位误差,K=

KφKvco为锁相环的环路增益。

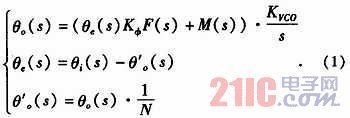

根据锁相环的相位模型,可以推导出经调制信号m(t)作用下环路的输出相位θo(s)的表达式。根据图2可得:

式中M(s)为m(t)的拉普拉斯变换。

为了分析方便,假定θi(s)=0,将(1)式整理可得:

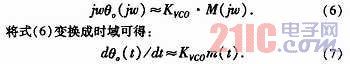

式中Kvco为常数,误差传输函数He(jw)具有高通特性。设调制信号m(t)的频谱范围为ΩL~ΩH,则当环路的截止频率远小于ΩL时,在ΩL~ΩH范围内有He(jw)≈l∠0°。此时式(5)可写成:

从上面的分析可得出结论:当环路工作于载波跟踪状态,即调制信号的频率远大于截止频率时,在调制信号频率范围内,环路的闭环频率特性近似为零。这样,环路对调制信号闭环一周的响应m’(t)约等于零,因而环路控制信号近似等于调制信号m(t)。也就是说,环路闭合后VCO的控制信号和开环近似相同,这就使VCO的频偏dθo(t)/d(t)正比于调制信号m(t),这样既可以实现Chirp超宽带信号的产生,同时又能保证载频的稳定。

2 基于锁相环的Chirp超宽带信号源的设计和实现

本文设计的Chirp超宽带信号源是基于锁相环的,锁相环的引入是这个设计的特色,其他调制部分电路可以用FPCA及高速DA器件简单实现,因此本节主要介绍电荷泵锁相环的设计。

设计中采用集成度高的可编程ADF4112芯片,该芯片中包含有鉴频鉴相器(PFD)、高精度电荷泵(CP)以及可编程的分频器(N),因此只需外加环路滤波器(LF)和压控振荡器(VCO)就可以构成一个完整的电荷泵锁相环电路。环路滤波器的设计是电荷泵锁相环电路中重要的部分,其设计的好坏直接影响到整个电路的性能。设计中采用的是有源滤波器,其中有源器件放在最后,这样有源器件不仅可以起到放大的作用,而且还起到了与加法器的隔离作用。但是有源器件的引入会增加带内的相位噪声,一般解决方法采用高阶滤波器来减少相位噪声。设计中采用有源三阶滤波器作为环路滤波器,电路结构如图3所示。

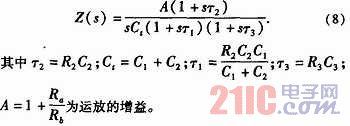

经分析可得有源三阶滤波器的传递函数为:

假设通过编程使ADF4112芯片中电荷泵的输出为正极性,则锁相环的开环增益为:

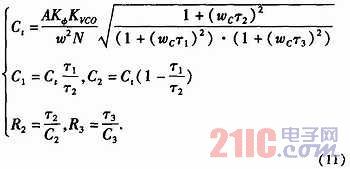

根据参考文献,若已知相位裕度φ、鉴相器增益Kφ、VCO的增益KVCO、环路带宽wc和T31(τ3与τ1的比值),则可算出:

当得到时间常数τ1、τ2、τ3后,则可计算出滤波器中各个元件的值。

C3一般取VCO输入电容的4倍至少为200 pF。

根据以上计算有源三阶环路滤波器参数方法,计算出各元件的值如表1所示。计算中取相位裕度为φ=45°;环路带宽200 kHz;鉴相频率为10 MHz;鉴相器的增益Kφ=5 mA;VCO的增益为Kvco=43.3 MHz/volt;VCO的输出频率Fout=580 MHz;有源器件运放的增益A=2。

根据上述设计结果,采用AD公司的环路滤波器设计软件ADIsimPLL,在鉴相频率为10 MHz、VCO振荡频率为580 MHz的条件下对该有源三阶环路滤波器进行仿真,仿真结果如图4所示。从系统的开环响应波特图可以看出,幅度增益为0 dB时,相位在-135°附近,有45°的相位裕量;相位在-180°时,幅度增益为-20 dB左右,由此可见该锁相环路是稳定的。

Chirp超宽带信号 锁相环 模拟法 相关文章:

- 全数字锁相环的设计及分析(03-01)

- 一种大电压输出摆幅低电流失配电荷泵的设计(04-22)

- 锁相环同步检波技术及在视频检波中的应用(05-20)

- 一种基于CMOS工艺的电荷泵锁相环芯片的设计(05-21)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环相位噪声与环路带宽的关系分析(08-04)