一种大电压输出摆幅低电流失配电荷泵的设计

时间:04-22

来源:EDN

点击:

0 引 言

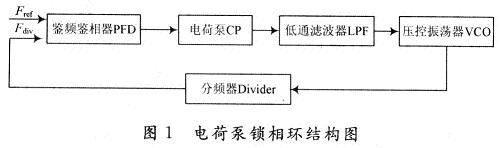

CMOS|0">CMOS电荷泵锁相环以其高速、低抖动、低功耗和易集成等特点,已广泛用于接收机芯片、时钟恢复电路中,如图l所示,电荷泵对整个电荷泵锁相环性能具有关键的作用,如果电荷泵的充放电电流能够在很大的输出电压范围内具有高精度的匹配,在PLL锁定某个频率时,LPF提供给VCO的控制电压将是一个常数,它将显著降低VCO输出频率的抖动,提高VCO的相位噪声特性,并且VCO可以具有很大的调谐范围。

l 传统电荷泵工作机制

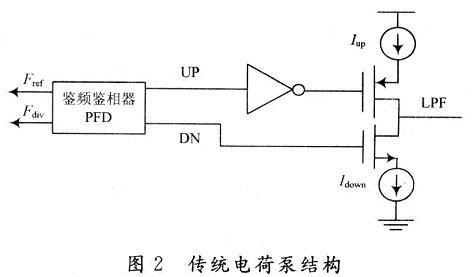

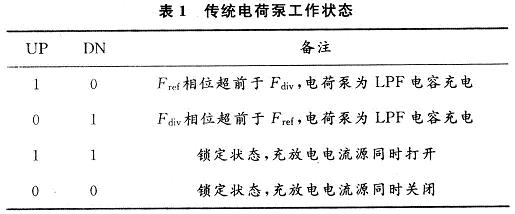

传统电荷泵结构如图2所示。

2 新型电荷泵设计

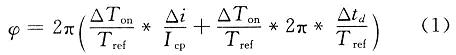

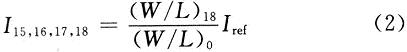

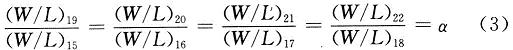

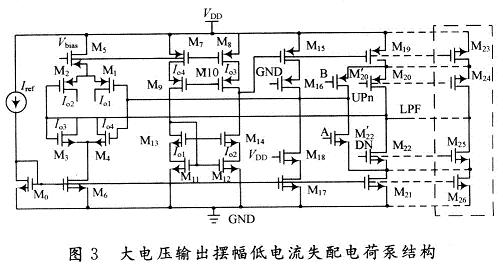

图3为本文提出的新型电荷泵结构,其中M1~M12构成一个一级的轨到轨运算放大器,M1和M2构成这个运算放大器的P管输入极,M3和M4构成N管输入级,M7~M12构成运放的电流求和电路,将差分输入产生的小信号电流转换成单端的电压输出,M15~M18构成这个运算放大器的第二级,M16的漏极接到:M1的栅极构成单位负反馈,因此可以保证M。和M2的栅极具有相同的电压,也就是说M15和M19具有相同的漏极电压,M17和M21也具有相同的漏极电压。M15和M18的栅极分别接到最低电位和最高电位,使这两个管子都工作在深线性区,所以M15~M18这条支路始终有电流,电流大小为:

(1)状态1:UP为高电平,DN为低电平,电荷泵为LPF充电开关管M20打开,M22关闭。由于运算放大器的存在,M15和M19的三个端口都处在相同的电位,因此I19=aI15电荷泵以aI15大小的电流对LPF电容充电。

(2)状态2:UP为低电平,DN为高电平,LPF通过电荷泵放电开关管M20关闭,M22打开。由于运算放大器的存在,M17和M21的三个端口都处在相同的电位,因此I21=aI17泵以aI17大小的电流对LPF电容放电。

(3)状态3:UP,DN同时为高电平,LPF输出电压保持稳定开关管M20,M22同时打开。在正常工作状态下,因为运放的存在,使得I21=aI17,I19=aI15,而I17=I15,因此I21=I19。M19中的电流全部从M21中流到地,因此LPF电容电压保持不变。

(4)状态4:UP,DN同时为低电平,LPF输出电压保持稳定开关管M20,M22同时关闭,此时A,B分别为高电平和低电平,控制开关管M21,M22同时打开,因此M19和M21的漏极电压都为LPF上的电容电压,克服了电荷共享。

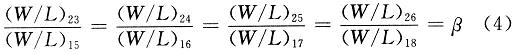

本结构还可以轻易地实现充放电电流的数字控制,如图3框内所示,假设:

CMOS|0">CMOS电荷泵锁相环以其高速、低抖动、低功耗和易集成等特点,已广泛用于接收机芯片、时钟恢复电路中,如图l所示,电荷泵对整个电荷泵锁相环性能具有关键的作用,如果电荷泵的充放电电流能够在很大的输出电压范围内具有高精度的匹配,在PLL锁定某个频率时,LPF提供给VCO的控制电压将是一个常数,它将显著降低VCO输出频率的抖动,提高VCO的相位噪声特性,并且VCO可以具有很大的调谐范围。

l 传统电荷泵工作机制

传统电荷泵结构如图2所示。

2 新型电荷泵设计

图3为本文提出的新型电荷泵结构,其中M1~M12构成一个一级的轨到轨运算放大器,M1和M2构成这个运算放大器的P管输入极,M3和M4构成N管输入级,M7~M12构成运放的电流求和电路,将差分输入产生的小信号电流转换成单端的电压输出,M15~M18构成这个运算放大器的第二级,M16的漏极接到:M1的栅极构成单位负反馈,因此可以保证M。和M2的栅极具有相同的电压,也就是说M15和M19具有相同的漏极电压,M17和M21也具有相同的漏极电压。M15和M18的栅极分别接到最低电位和最高电位,使这两个管子都工作在深线性区,所以M15~M18这条支路始终有电流,电流大小为:

(1)状态1:UP为高电平,DN为低电平,电荷泵为LPF充电开关管M20打开,M22关闭。由于运算放大器的存在,M15和M19的三个端口都处在相同的电位,因此I19=aI15电荷泵以aI15大小的电流对LPF电容充电。

(2)状态2:UP为低电平,DN为高电平,LPF通过电荷泵放电开关管M20关闭,M22打开。由于运算放大器的存在,M17和M21的三个端口都处在相同的电位,因此I21=aI17泵以aI17大小的电流对LPF电容放电。

(3)状态3:UP,DN同时为高电平,LPF输出电压保持稳定开关管M20,M22同时打开。在正常工作状态下,因为运放的存在,使得I21=aI17,I19=aI15,而I17=I15,因此I21=I19。M19中的电流全部从M21中流到地,因此LPF电容电压保持不变。

(4)状态4:UP,DN同时为低电平,LPF输出电压保持稳定开关管M20,M22同时关闭,此时A,B分别为高电平和低电平,控制开关管M21,M22同时打开,因此M19和M21的漏极电压都为LPF上的电容电压,克服了电荷共享。

本结构还可以轻易地实现充放电电流的数字控制,如图3框内所示,假设:

则可以通过2个比特控制充放电电流的三种可能(另一种充放电电流的可能为0 mA),分别为:aIref,βIref,(α+β)Iref,这在PLL的设计中具有实际意义,因为充放电电流的大小直接影响PLL的带宽口,因此可以根据实际情况调整电荷泵的充放

则可以通过2个比特控制充放电电流的三种可能(另一种充放电电流的可能为0 mA),分别为:aIref,βIref,(α+β)Iref,这在PLL的设计中具有实际意义,因为充放电电流的大小直接影响PLL的带宽口,因此可以根据实际情况调整电荷泵的充放

- 德州仪器高性能模拟运放产品系列介绍集锦(11-13)

- CMOS求和比较器在PWM开关电源控制中的应用(11-27)

- 如何将CMOS LDO应用于便携式产品中(01-15)

- 2.5 Gb/s 0.35μmCMOS光接收机前置放大器设计(01-22)

- 用于下一代移动电话的电源管理划分(08-28)

- 不同电源供电的器件间的桥接(04-27)