一种基于LMX2485E芯片的调制倍频电路

摘要:本文介绍了一种调制倍频单元的设计工作。电路中选用了一种具有跳频功能、可通过编程精确预置带有小数的倍频系数的高分辨率频率合成器芯片,同时实现数字调制、锁相倍频的功能,直接取代原有模拟调制、倍频电路。

关键词:频率合成器;数字调制;锁相倍频;相位噪声

某项目整机小型化要求电路系统体积配合减小,经过分析,电路系统体积减小的关键在于将分立元件众多的模拟调制倍频单元电路替换为数字集成电路。本文的主要工作就是寻找模拟倍频电路的数字化替换方案,简化倍频单元设计。

技术方案选定

调制倍频电路需要生成带有调制信息的6834.6875MHz左右的微波探询信号,主要通过微波腔中对6840MHz和尾数5.3125MHz信号下混频实现, 6840MHz信号的获取首先是将10MHz参考源信号通过半导体分立元件搭建的9倍频三极管选频、放大电路生成90MHz信号,再通过快恢复阶跃二极管进行高次谐波倍频,利用微波腔对76次谐波进行谐振后获取6840MHz信号。5.3125MHz信号则是通过数字逻辑电路将10MHz参考源信号分别生成5MHz和0.3125MHz信号,再进行合频、滤波、选频放大输出。对6840MHz进行调制或对5.3125MHz信号进行调制都是可行的,一种是先对10MHz参考源信号进行调制,6840MHz或5.3125MHz信号就带有了调制信息;另一种是利用具有数字调制功能的DDS芯片合成具有调制信息的5.3125MHz信号后与6840MHz信号混频使用。本文采用对6840MHz调制的方案,工作原理图如图1所示。

在原有方案中,6840MHz信号的前端调制电路和9倍频选频电路多为纯模拟方案,分立元件众多、调试复杂,不利于小型化;而且不论采用哪一种调制方式,5.3125MHz综合电路、微波混频电路都必不可少,增加了电路的复杂程度。若不改变技术方案,直接在原有方案基础上进行电路小型化是比较困难的。

从另一个角度考虑,由于快恢复阶跃二极管只能够产生整数次谐波,那么如果馈入它的激励信号是一个已经含有尾数频率的调制信号,从理论上讲,经过高次倍频后被微波腔谐振选频,也可以得到带有调制信息的6834.6875MHz信号。经过计算,选择455.645833MHz信号作为快恢复阶跃二极管的激励信号,因为该信号经过15倍频直接对应6834.6875MHz信号。该技术方案的选定有几个好处:第一可以节省5.3125MHz综合电路、混频电路;第二由于快恢复阶跃二极管倍频次数减少,可以降低激励功率、提高倍频效率;第三由于该方案将引入数字集成芯片,摒弃传统分立元件搭建的调制、倍频、混频方案,使电路引入数字化、小型化成为可能。故本文所采用的技术方案就是利用数字集成芯片输出带调制信息的455.645833MHz激励信号,直接进行15次阶跃管微波谐振选频,生成带有调制信息的6834.6875MHz微波探询信号。工作原理图如图2所示。

经过器件选型,采用基于快速锁相环技术、带调制功能的小数频率综合器LMX2485E实现该技术方案。

LMX2485E频率合成器工作原理

频率合成器的基本原理:应用数字逻辑电路把压控振荡器输出频率一次或多次分频至鉴相器输入频率上,再与参考频率在鉴相电路中比较,反映相位、频率差异的误差信号经过环路滤波器后以缓变的直流信号来控制压控振荡器频率,如图3所示。

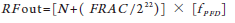

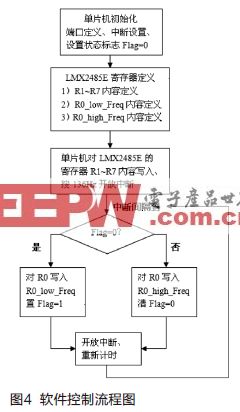

LMX2485E芯片内部的分频系数是由单片机编程控制,包含整数和小数两部分,这意味着写入合适的分频系数后,输入10MHz参考信号,从压控振荡器端可以直接输出455.645833MHz信号,即分频系数为45.5645833,根据芯片手册的要求将45写入整数寄存器中,将5645833写入小数寄存器中即可。控制压控振荡器输出频率计算公式(1)如下:

这里,RFout是经过倍频控制后的压控振荡器频率输出;

N是倍频系数中的整数部分;

FRAC是倍频系数中的小数部分的寄存器控制字;FRAC/222是倍频系数中的小数部分;

fPFD是鉴相频率输入,本方案中为高稳恒温压控晶振输出的10MHz参考信号。

配合选用不同频段的外部压控振荡器,LMX2485E芯片的倍频工作范围50MHz~3GHz。芯片外部输入的信号有标准频率源参考信号和压控振荡器输出反馈频率以及接口控制信号。压控振荡器输出频率经过耦合电路输入到LMX2485E后,经11位整数分频器和22位小数分频器的配合使用得到分频后的鉴相输入频率,进入鉴相器的B相。标准频率源参考信号经过耦合电路输入到LMX2485E后进入鉴相器的A相(可根据需要使用6位分频器改变鉴相频率)。控制信号由片选信号CE、时钟信号CLK、数据信号DATA和数据锁存信号LE组成。在时钟信号的控制下,控制字由DATA口输入R0至R7寄存器中。在接收到数据锁存信号后,先前输入的R0至R7寄存器内容到达对应的锁存

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 直接数字频率合成器的实现设计方案(03-01)

- 基于DDS芯片和集成锁相芯片构成的宽频合成器设计(05-25)

- 基于单片机与FPGA的直接频率数字合成器的设计方案(02-23)