一种基于LMX2485E芯片的调制倍频电路

器,本次频率控制参数设置生效。鉴相器输出的误差信号通过滤波环路后控制外部的压控振荡器的输出频率,使10MHz高稳晶振输出频率的稳定度能够传递到压控振荡器的输出频率上,最终使455.645833MHz信号也具备相同的频率稳定度。同时,该频率合成器具备快速锁定功能,在环路参数设置正确的情况下,从新的频率控制字写入到压控振荡器稳定输出新的频率,只需5ms,本文的调制速率为136 Hz,两个频率跳变间隔为8ms左右,经试验证明完全能够满足调制要求。

寄存器配置及软件流程

LMX2485E有R0~R7这 8个24位寄存器,R1关联着分频系数中的整数部分;R0关联着分频系数中的小数部分。由于本文中受调制切换的左、右两个频率值相差40 Hz,所以只改变小数寄存器R0内容即可,剩余 R1~R7寄存器按照手册要求在程序初始化时一次写好后就不需改动。

对于本方案中,调制信息表现为以455.645833MHz信号为中心频率,以136Hz的速率(调制速率)在两个频率点之间切换,两个频率点与中心频率相差±20Hz(该指标对应调制深度)。那么左边频点写入455.645813MHz的频率控制字,右边频点写入455.645853MHz的频率控制字,单片机按136 Hz的中断速率控制芯片刷新频率控制字即可实现频率调制要求。按照这个思路,软件流程图编写如图4。

硬件连接与参数设定

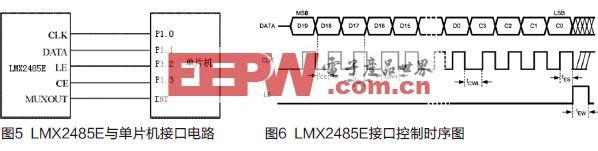

LMX2485E的硬件电路有比较成熟的参考应用,与单片机接口电路如图5所示。芯片手册给出的时序控制图如图6所示。

接口控制有几点注意事项:片选使能CE信号在上电后置高电平;DATA和CLK信号遵从SPI通信协议,数据在CLK上升沿有效;数据锁存信号LE在某个寄存器控制字节全部写完后才能置高,保持足够时间后拉低。

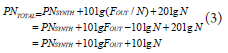

该芯片的MUXOUT管脚可通过软件设置为锁定检测输出端,高电平表示锁定、低电平表示脱锁。使用单片机的外部中断检测口或搭建如图7所示的锁定状态检测电路,可以准确获知产生455.645833MHz信号的锁相环路是否工作在正常状态。这对于快速判断6834.6875MHz微波探询信号是否工作正常很有帮助。

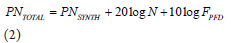

锁相环频率合成器输出的相位噪声TOTALPN与鉴相频率PFDF以及反馈分频系数N之间的关系如公式(2)所示。

其中, TOTALPN为锁相环频率合成器输出的总相位噪声,SYNTHPN为锁相环频率合成器自身的相位噪声,N为反馈分频系数,PFDF为/FoutN,Fout为环路输出频率。由公式(2)可得公式(3)

在SYNTHPN和Fout一定的情况,鉴相频率PFDF越大,则反馈分频系数N越小,于是环路噪声越低。本文中标准频率源为10MHz信号,LMX2485E芯片允许最大鉴相频率为50MHz,故本文取鉴相频率PFDF为10MHz。查阅手册可知SYNTHPN最大为-210dBc/Hz,根据Fout为455.645833MHz,N为45.645833可求得该锁相环路理论最优相噪为-108 dBc/Hz。

控制压控振荡器的环路滤波器参数可以通过ADIsimPLL 3.1软件进行仿真,使用与仿真给出的推荐元件参数相同或相近的值后就可投入使用。根据相关应用笔记,滤波器选择为三阶无源低通滤波器,环路带宽选择原则为不超过鉴相频率的1/10,本文鉴相频率为10MHz,根据实验结果,取环路带宽100kHz左右。

锁相倍频电路实验结果

使用安捷伦E4408B频谱仪得到LMX2485E锁相环路输出信号经过放大、阻抗匹配后如图7所示频谱图。

在设定左、右旁瓣频点与中心频率差值后,左、右旁瓣频点在程序控制下开始定时切换。在频谱仪上会看到输出信号左、右旁瓣频点与中心频率存在功率偏差。通过实验比对发现,频率偏差愈小功率偏差愈大,频率偏差愈大功率偏差愈小。同时,由于调制速率、调制深度均通过软件程序灵活设定,这个优点在原有模拟方案中也是难以实现的。

该单元电路输出的信号经过对比测试,其频谱质量、谐波抑制、相位噪声均好于原有方案,而且由于调制参数、倍频系数均可通过编程设定,极大简化了调试过程,提高了电路集成度。

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS+PLL技术的频率合成器的设计(07-23)

- 直接数字频率合成器的实现设计方案(03-01)

- 基于DDS芯片和集成锁相芯片构成的宽频合成器设计(05-25)

- 基于单片机与FPGA的直接频率数字合成器的设计方案(02-23)