基于SRAM芯片立体封装大容量的应用

静态随机存储器(static RAM),简称SRAM。在电子设备中,常见的存储器有SRAM(静态随机访问存储器)、FLASH(闪速存储器)、DRAM(动态存储器)等。其中不同的存储器有不同的特性,SRAM无需刷新电路即能保存它内部存储的数据。而DRAM每隔一段时间,要刷新充电一次,否则内部的数据即会消失。与SDRAM相比,SRAM不需要时钟信号,即可保持数据不丢失。

1、VDMS16M32芯片介绍

VDSR16M32是一款工作电压3.3V,16Mbit,32位数据总线的立体封装SRAM模块芯片,由4个256K x 16bit的SRAM芯片堆叠而成。整个模块采用立体封装堆叠技术,它们之间的互相连接线非常短,寄生电容小。

1.1 芯片的内部功能结构和外部引脚

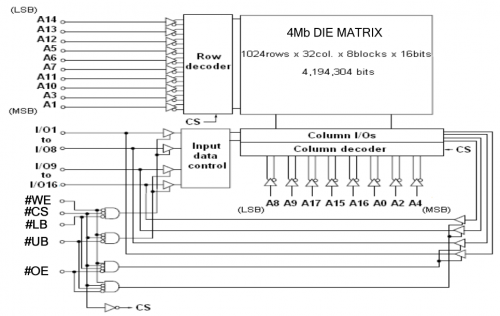

图1是立体封装的大容量芯片VDSR16M32中每一片SRAM的内部结构和功能框图,由MEMORY存储矩形阵列,列译码器、行译码器、数据控制和控制逻辑等部分组成。

图1 VDSR16M32中SRAM的内部功能结构框图

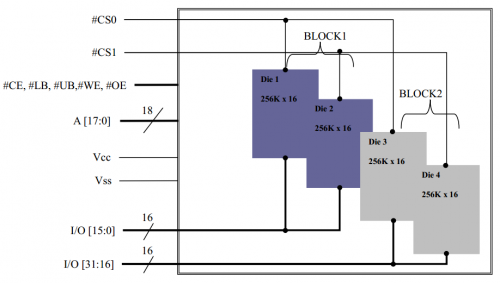

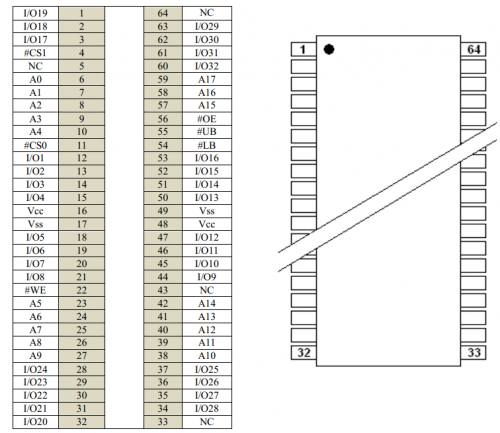

图2是立体封装的大容量存储芯片VDSR16M32的内部结构和功能框图,图3是VDSR16M32的外部引脚分布图,其中A【0:17】是地址输入信号引脚,#CS0、#CS1是芯片里面BLOCK1和BLOCK2的选择引脚,#OE是芯片的输出启用引脚,#WE是芯片的写入启用引脚,#LB是低16位的选择信号,#UB是高16的选择信号,I/O【0:31】是芯片的数据线,其中数据线D【0:15】为BLOCK1的数据输入输出引脚,数据线D【16:31】为BLOCK2的数据输入输出引脚,VCC为电源引脚,VSS为接地引脚。

图2 立体封装的大容量芯片VDSR16M32的功能结构框图

图3 VDSR16M32的外部引脚分配图

VDSR16M32的引脚的功能如表1所示:

| 管脚 | 名称 | 功能 |

|---|---|---|

| #CS0 | Chip select | Disables or enables memory die1 and 3 operation |

| #CS1 | Chip select | Disables or enables memory die2 and 4 operation |

| A0-A17 | Address | Row/column 18-bit addresses |

| #WE | Write enable | Enables write operation common to all dies |

| #OE | Output enable | Enables data output common to all dies |

| #UB | Upper byte select | Latches upper bytes addresses common to all dies |

| #LB | Lower byte select | Latches lower bytes addresses common to all dies |

| I/O1-I/O32 | Data input/output | Data I/O1 to I/O16 activated from dies 1 and 2 and Data I/O16 to I/O32 activated from dies 3 and 4 |

| Vcc/Vss | Power supply/ground | Power and ground for the input/output buffers and core logic. |

| NC | No connection | This pin is recommended to be left No Connection on the device. |

表1 VDSR16M32的引脚的功能

1.2 芯片的主要特性

1、访问周期:最小12ns;

2、不需要时钟信号;

3、兼容TTL电平;

4、数据至少可以保持20年;

5、由两个256K*32bit的块组成;

6、由5片4Mbit SRAM 堆叠而成;

7、2个独立片选#CS0,#CS1; 8、

8、工作电压:3.3V;

9、64脚TSOP封装。

1.3 芯片的操作

芯片VDSR16M32的工作模式和SRAM差不多,都具有读写操作模式,关于芯片VDSR16M32的操作模式的真值表如下图4所示:

图4:VDSR16M32的工作模式的真值表

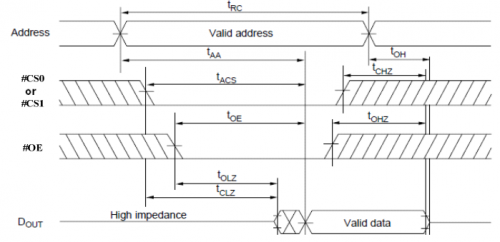

VDSR16M32的读操作非常简单,当片选#CS0或者#CS1和输出启用引脚#OE都为低电平时,芯片进行读操作,即可从芯片读出数据。VDSR16M32芯片的读操作时序图如图5所示:

图5 VDSR16M32芯片的读操作时序图

VDSR16M32芯片的读取操作步骤如下:

1) 通过地址总线把要读取的bit的地址传送到相应的读取地址引脚(这个时候/WE 引脚应该没有激活,所以SRAM 知道它不应该执行写入操作) 。

2) 激活#CS0或者#CS1选择该芯片的BLOCK0或者BLOCK1。

3) 激活#OE引脚让VDSR16M32知道是读取操作。

第三步之后,要读取的数据就会传输到数据总线。

VDSR16M32的写操作同读操作类似,当片选#CS0或者#CS1和写入启用引脚#WE都为低电平时,芯片进行写操作,即可写入数据到芯片中区。VDSR16M32芯片的写操作时序图如图6所示:

- 基于位线循环充电SRAM模式的自定时电路设计 (10-03)

- 使用FPGA器件最大限度地降低高速DSP密集型系统设计的功耗(07-12)

- Maxim为什么选择设计单片NV SRAM模块(11-04)

- 从Flash和SRAM中触发中断的过程示例(二)(09-24)

- 从Flash和SRAM中触发中断的过程示例(一)(09-24)

- RTN的SRAM误操作进行观测并模拟的方法简介(09-03)