RTN的SRAM误操作进行观测并模拟的方法简介

瑞萨电子开发出了对起因于随机电报噪声(RTN:Random Telegraph Noise)的SRAM误操作进行观测并实施模拟的方法。利用该方法可高精度地估计22nm以后尖端LSI中的RTN影响,适当设定针对RTN的设计余度。该公司已在“2010 Symposium on VLSI Technology”(2010年6月15~17日,美国夏威夷檀香山)上发表了该成果(论文编号:18.1)。

RTN是一种因晶体管载流子被栅极绝缘膜等中的陷阱捕获或释放,而使晶体管阈值电压随时间随机变动的现象。业界普遍预测,今后随着微细化的发展,RTN将成为导致LSI工作故障的主要原因。瑞萨此前一直在推进RTN的分析及模型化研究。目前已在RTN公式化以及陷阱能级分布的推测方法等方面取得了成果。

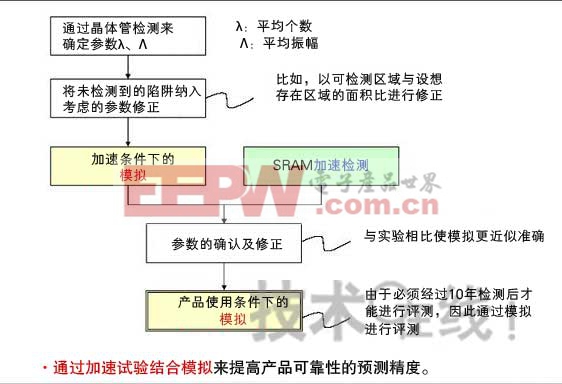

此次该公司以SRAM为对象,开发了用于分析RTN对电路工作造成的影响,并将分析结果体现在芯片设计中的方法(图1)。该方法由三项要素构成:(1)对起因于RTN的SRAM误操作进行观测,掌握其发生概率的方法,(2)在实用时间内对误操作发生的概率进行模拟的方法,(3)使加速试验的结果体现在模拟中,以提高精度的方法。此次使通过(2)、(3)方法导出的计算结果与(1)加速试验的结果实现了充分吻合。在这一方面,值得一提的是以下两点。第一,瑞萨以前一直在探讨的RTN分析式在预测起因于RTN的电路误工作时有效。第二,今后通过提高加速试验的规模及精度,并体现其结果,便有望将模拟精度提高到实用水平。

下面分别介绍一下(1)、(2)、(3)的概要。

观测与模拟的结果充分吻合

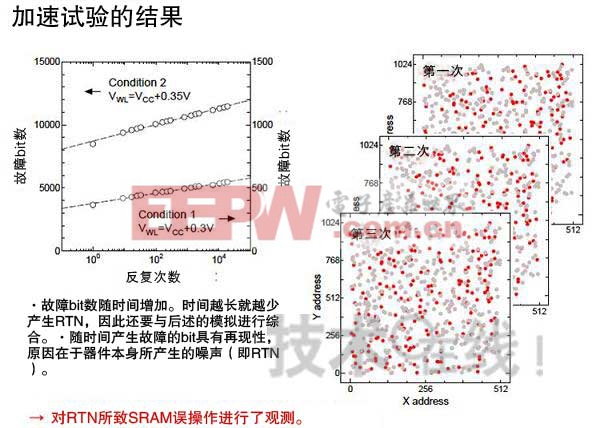

(1)以电路水平观测起因于RTN的误操作,可以说这是一项对RTN的影响进行评估的基本操作。不过,如果是目有微细化水平的芯片的话,RTN所致误操作的发生频率非常低,很难进行观测。因此,瑞萨采用了有意减小SRAM的工作余度,提高RTN所致误操作频率的方法(图2)。即加速试验方法。具体而言,就是通过降低SRAM电源电压,提高字线电压,来减少读取数据时的工作余度。通过在这种状态下反复读取数据,使RTN所致误操作频发。

该加速试验的结果表明,在发生工作故障的bit数的读取次数增加的同时,其增加倾向与(2)中所述模拟导出的倾向相吻合(图3)。而且,该加速试验中生产故障的bit还具有再现性。从这些结果可以推侧,由此观测到的工作故障起因于器件内部存在的,且随时间变动的偏差,即RTN。

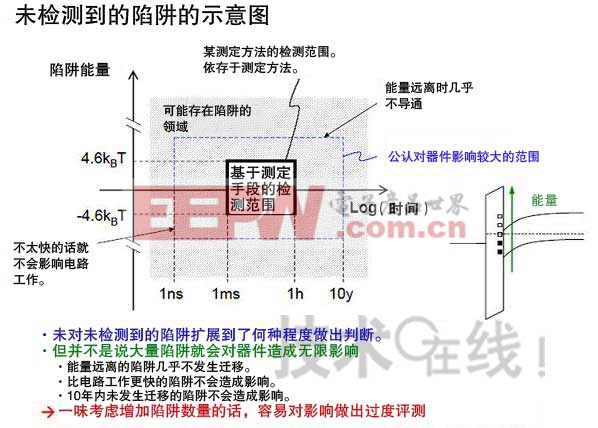

从(2)来看,一般很难以分析式导出RTN所致SRAM误操作的概率。其原因在于,RTN尽管是依存于时间的现象,但却无法获得包括时间项在内的完全分析式。因此,使用模拟手段,将时间项作为参数导入计算的方法十分有效。该方法的优点在于,可在计算中将普通陷阱检测方法因时间常数及能量过大或过小而无法检测的“看不见的陷阱”纳入考虑(图4)。

此次瑞萨开发了根据陷阱个数、振幅(陷阱引起的特性变动的幅度)及时间常数(捕获和释放电荷的时间间隔)的统计学分布,以蒙特卡罗法对一定时间(比如想保证的产品寿命)内晶体管及电路所产生的特性变动的最大值进行计算的方法(图5)。将以往RTN分析式未考虑的陷阱时间常数和能量作为参数进行了导入。该计算方法不进行严密的电路模拟,只进行概率的计算和振幅的加算。因此,可在实用时间内进行模拟。

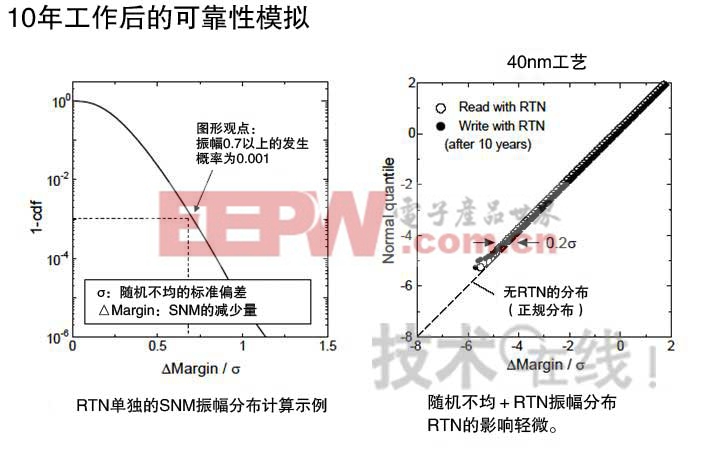

该公司为了获得SRAM中RTN所致误操作的发生概率,对6个晶体管构成的组件使用了此次了模拟方法,并根据结果算出了作为SRAM工作稳定性指标的SNM(Static Noise Margin)的变化量。对40nm工艺SRAM进行该变化量的计算后表明,在该工艺中,与杂质不均相比,RTN的影响较为轻微(图6)。

从(3)来看,在模拟中体现加速试验的结果以提高精度的手段对于将此次的方法应用于实际的芯片十分重要。这源于各晶体管中存在的陷阱个数、振幅及时间常数等无法通过测定手段来完全掌握。

此次的模拟方法,其计算结果会因为作为参数的陷阱时间常数和能量存在分布如何进行假设,以及计算中将其纳入考虑的范围有多大而发生变化。因此,瑞萨以提高模拟精度为目标,开发了使加速试验结果在模拟参数的设定中得到体现的方法。具体而言,就是从加速试验开始考虑SRAM的故障bit数是以何种趋势随着工作次数而增加的,并以能够在模拟中再现这种趋势为目的,修正与陷阱时间常数和能量存在分布相关的假设。

- 基于位线循环充电SRAM模式的自定时电路设计 (10-03)

- 基于SRAM芯片立体封装大容量的应用(02-14)

- 使用FPGA器件最大限度地降低高速DSP密集型系统设计的功耗(07-12)

- Maxim为什么选择设计单片NV SRAM模块(11-04)

- 从Flash和SRAM中触发中断的过程示例(二)(09-24)

- 从Flash和SRAM中触发中断的过程示例(一)(09-24)