解决DSP设计面临的终极挑战

多年来,数字信号处理器 (DSP) 设计人员一直在应付这样一项艰难的工作:提供占用空间小的高性能芯片,而且要不影响灵活性和软件的可编程能力。

由于新的应用程序发展速度惊人,提供的 DSP 必须在功率、性能和使用寿命上跟上这种速度,应对当前面临的挑战,并准备好应对未来的应用。这些高性能多核心 DSP被越来越多地应用在电信接入、改进数据率GSM服务(EDGE)和基础设施设备领域,用来处理语音、视频和无线电信号。

以前,电信设备制造商使用专用的 ASIC 或 DSP-ASIC 组合来达到自己的目标。现在,这些新的 DSP 可以替代那些繁琐的解决方案;如果足够强大,它们还可以实现以前的解决方案所无法实现的灵活性。对于那些必须在网络部署中持续使用多年的接入和基础设施设备,而言, 这些灵活的解决方案是大有裨益的。假如这些类型的设备和应用程序的使用寿命得到延长,那么,成功的关键就是灵活性、适应性和现场可编程性。

在目前的技术条件下,ASIC 在灵活性或现场可编程性方面不如 DSP,但 DSP 的能耗较大,这让芯片设计人员左右为难。不过,还是有希望:新一代的多核心 DSP 可以同时做到高性能和高能效。做到这点的技术是存在的,但必须先解决"功率耗散"(功率极限)问题。

功率极限

目前,芯片功率耗散的源头有两个:以泄漏形式出现的静态现象;以开关运算形式出现的动态现象。在采用 90 纳米和以下工艺的 CMOS 技术中,这种功率耗散现象最为明显。但是,新一代的 DSP 设计不仅能减轻和避开这种功率极限,而且实际上可以提高基础设施、接入和 EDGE 设备的处理能力,同时限制功率消耗和热量耗散。

部分特定CMOS 技术下的能耗界定的关键度量指标:

•电源电压

•门开关速度

•门输入电容

•门功耗

•每个 MAC 运算消耗的能源

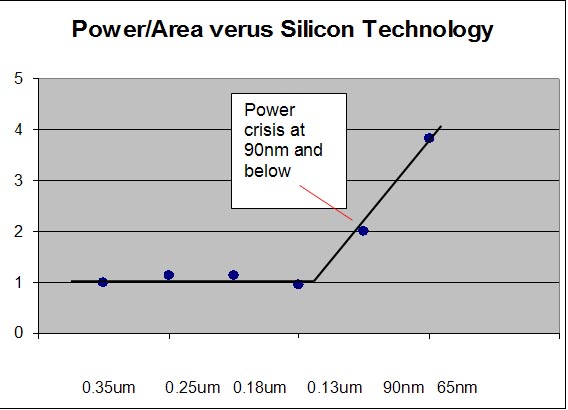

研究表明,同等功能(如 MAC 单元)的功率密度(即单位面积的功率)在 0.13 微米(含)以上的芯片中相当稳定。但是,到达 90 纳米时,这个指标会突然升高。

Power/Area versus Silicon Technology

功率/面积与硅技术

Power crisis at 90 nm and below

90 纳米及以下工艺的功率极限

um

微米

nm

纳米

在采用 0.13 微米技术以前,DSP 设计能够在提高性能的同时降低功率,从而可以在单个芯片中植入更多的电路。这主要是通过减小尺寸并降低电压实现的。采用了 90 纳米技术后,所有这一切就都行不通了。

现在面临的是以性能换功能的问题,这是设备制造商所不愿遇到的情况:在一个芯片中植入更多电路但降低性能,或者减少电路数以减少功能。

由于"功率极限"的情形继续存在,设计人员一直在通过增加功耗来获得性能和功能方面的优势。但是,这会带来一种新的风险:达到热量耗散的极限。所产生的问题可能已经在当前市场上最新一代的通用多核心 DSP 中出现。

零-和博弈:静态能效

因为性能是基础设施、接入和 EDGE 应用的主要目标,因此设计人员一般并不关心零待机功率问题。因此,通常采用通用硅工艺来优化性能,而不会选择低泄漏的硅。选择低泄漏的硅可以降低待机功率,但也会降低速度和性能。

这就要求有选择地使用晶体管。

在使用电池的设备中,高电压阈值 (HVT) 可能是最佳的;但在基础设施应用中,首选的是标准电压阈值 (SVT) 技术。

例如,假如某个设计使用 HVT 逻辑运算,并且电源电压为 1.2V,则将连续产生 20mW 的泄漏功率。如果以最大容量运算,则将消耗 1W 的动态功率。

使用 SVT 逻辑运算的相同设计在电源电压为 1.0V 时可以实现几乎相同性能,产生的泄漏功率多出 4 倍 (100mW),但动态消耗的功率只有 694mW (1.02 /1.22 = 0.694)。

因此,泄漏较高的 SVT 设计消耗的总功率只有 790mW,而相比之下,HVT 设计的消耗总功率为 1.02W。前者比后者节能 23%。

HVT 设计和 SVT 设计的功耗比较

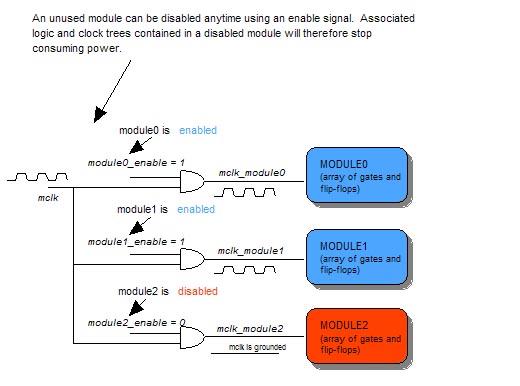

An unused module can be disabled anytime using an enable signal. Associated logic and clock trees contained in a disabled module will therefore stop consuming power.

可以使用激活信号随时禁用未使用的模块。被禁用的模块中包含的相关逻辑和时钟树会因此停止消耗能量。

An unused module can be disabled anytime using an enable signal. Associated logic and clock trees contained in a disabled module will therefore stop consuming power.

可以使用激活信号随时禁用未使用的模块。被禁用的模块中包含的相关逻辑和时钟树会因此停止消耗能量。

module0 is enabled

module0 已激活

module1 is enabled

module1 已激活

module2 is disabled

m

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 达芬奇数字媒体片上系统的架构和Linux启动过程(06-02)

- FPGA的DSP性能揭秘(06-16)

- 用CPLD实现DSP与PLX9054之间的连接(07-23)

- DSP+FPGA结构在雷达模拟系统中的应用(01-02)