达芬奇数字媒体片上系统的架构和Linux启动过程

达芬奇(DaVinci)数字媒体技术平台TMS320DM6446/3采用了ARM+DSP双核的架构,本文从芯片的硬件结构入手介绍达芬奇DMSoC硬件部分及Linux OS的启动过程。

达芬奇DMSoC硬件概述

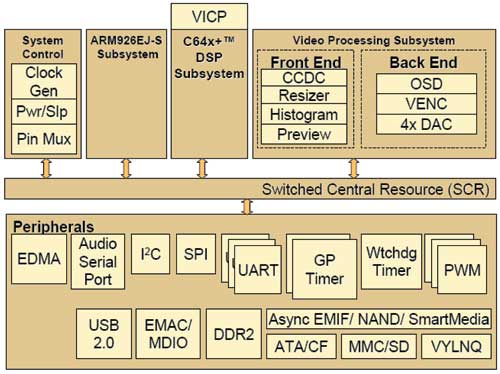

如图1所示,达芬奇数字媒体片上系统(DMSoC)提供:两个内核(ARM+DSP);视频处理子系统(VPSS);多种Boot模式(NOR Flash/NAND Flash/UART0 Boot Mode);两个电源域;多个时钟树;多个引脚独立或复用的外设。

图1 DM6446功能结构框图

● ARM-DSP集成

对于双核的达芬奇架构,大家最关心的就是两个核之间的资源分配、通信方式及如何高效地实现资源共享各尽其能。ARM独享(DSP不可用)的外设有:UART0/1/2,I2C,看门狗定时器,PWM0/1/2,ARM中断控制器,USB2.0,ATA/CF,SPI,GPIO,VPSS,EMAC/MDIO,EMIFA CONTROL,VLYNQ,MMC/SD。DSP独享(ARM不可用)的外设有:DSP中断控制器,VICP。ARM和DSP共享的外设有:EDMA,Timer0/1,Power & Sleep Controller,ASP和EMIFA Data。

图2 ARM-DSP集成结构

如图2所示,可以很清楚地看到ARM可以访问DSP片内存储器(L2RAM和L1P/D);DSP可以访问ARM片内存储器;ARM和DSP共享DDR2和AEMIF。因此,通常情况下ARM只需传递需要处理的数据地址指针给DSP,而无须大块的数据搬移。ARM和DSP之间的通信可以通过相互中断实现。ARM可以中断DSP(通过4个通用中断和1个不可屏蔽中断);DSP可以通过2个通用中断来中断ARM。ARM控制DSP的电源、时钟、复位和引导。

● DMSoC存储器映射

达芬奇DMSoC多个片上存储器和两个处理器及不同的子系统相关。为了简化软件开发,DMSoC中所有的存储器统一编址,如表1所示。

● DMSoC交换中心资源

以上大家看到DMSoC有非常丰富的外设和视频处理硬件资源,而且ARM和DSP又共享DDR2等存储器资源,那么DMSoC又是如何确保ARM、DSP和VPSS同时访问外设或存储器资源时不会引起冲突呢?DMSoC中的交换中心资源(SCR:Switched Central Resource)会做出管理。如图3所示,把任何一个发起数据传输的源称为Master(每一个Master有一个专用的ID),这个Master要访问的目的地称为Slave,这样在Master和Slave之间就构成一条数据传输的通路。从图3中可以看到,在SCR中可以有很多并行的Master到Slave的数据通路。如果是不同的Master、相同的Slave,那么可以通过设置每一个Master的优先级来得到特殊应用系统的最佳性能。对于大多数的Master,可以通过寄存器MSTPRI0和MSTPRI1来设置它们的优先级。如果Master是C64x+、VPSS和EDMA,可以通过它们自己的相关寄存器控制它们自己的优先级,这样可以更加灵活、快速的实现高的视频数据吞吐带宽。详细信息可以参考DM6446的数据手册。

图3 DMSoC交换中心资源的结构框图

电源域及复位

达芬奇DMSoC有两个电源域,分别是Always On域和DSP域。Always On域由CVDD ARM核电源供电,给ARM、总线、SCR和除VICP之外的所有外设提供电源;DSP电源域由CVDDDSP DSP核电源供电,给DSP和VICP提供电源。

双核架构的达芬奇DMSoC的功耗也非常有竞争力,这一方面取决于芯片本身的工艺,另一方面也取决于芯片内部时钟和电源的结构。如图4所示,达芬奇DMSoC有电源休眠控制器(Power & Sleep Controller)管理芯片电源的开关及复位。可以用软件控制DSP电源域,控制DSP及其模块时钟的开关和复位。PSC不支持ARM及其模块的断电控制、ARM的本地复位和ARM的时钟关断控制。同时PSC可以中断ARM和DSP,支持IcePick仿真(emulation)特性。

图4 DM6446的电源休眠控制器

关于达芬奇DMSoC的复位类型、触发源及对应的复位对象请参考表2。

达芬奇DMSoC初始化流程

● 达芬奇DMSoC复位状态

DM644x上电复位后,芯片的绝大部分模块都处于不工作状态。锁相环PLL处于旁路(Bypass)模式;DSP子系统的状态取决于DSP_BT引脚;UART1和UART2也处于不工作状态,UART0的状态取决于BTSEL引脚(如果BTSEL=11,UART0工作);EMIFA处于工作状态,其数据总线宽度由EM_WIDTH决定,地址总线宽度由AEAW决定;芯片的大部分引脚都被配置为GPIO引脚。引脚复用通过寄存器PINMUX0和PINMUX1控制。

● 达芬奇DMSoC初始化顺序

(1)DMSoC复位。芯片的配置由PSC决定,取决于BTSEL[0-3]、EM_WIDTH、AEWA和DSP_BT的状态。

(2)ROM boot loader(如果被选)。NAND或者UART0的初始化。

(3)引导加载(Boot-loading)。以U-boot为例,①使能电源域:DDR2和DSP;②设置时钟频率(ARM、DSP和DDR2时钟的乘除系数);③设置引脚复用控制器;④设置ARM引导启动操作系统。

(4)操作系统启动。以Linux为例,①初始化ARM;②初始化硬件系统;③初始化Linux环境。

● U-boot初始化顺序

通常情况下,ARM Linux要求boot loader中有少许的初始化。目前TI的DVEVM使用的是U-boot-1.1.3。U-boot代码中首先运行的是u-boot/cpu/arm926ejs/start.S,芯片和一些DVEVM板的硬件配置主要在u-boot/board/davinci/platform.S和davinci.c中完成。其中u-boot/board/davinci/platform.S设置最基本的系统硬件环境,包括系统PLL及DDR2的初始化、PSC的配置及使能UART0、AEMIF等硬件模块。有些工程师设计的达芬奇板可能用到了和DVEVM不同的Flash,那么就要根据用到的Flash参数修改u-boot/board/davinci/flash.c。另外,关于DM644x支持的NAND Flash ID,请参考TMS320DM644x DMSoC的相关文档。

以NOR Flash boot为例,DVEVM u-boot初始化下列的达芬奇DMSoC内容:

达芬奇 TMS320DM6446 3 ARM+DSP Linux OS 相关文章:

- 基于达芬奇技术的数字视频系统设计与实现(05-08)

- 数字电影放映系统实现方案(12-20)

- 基于DM368的视频捕获与编解码系统设计(09-12)

- 奇偶科技采用TI达芬奇DSP开发车牌识别系统(03-12)

- 一种数字视频技术简介-达芬奇技术(03-12)

- 什么是达芬奇(DaVinci)技术(12-07)