基于FPGA的实时金融指数行情并行计算

30 40 50 60 70 80 100

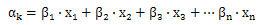

将上面计算方法进行抽象可以得到:

(2)

(2)

其中xn为从股票信息中抽象出的向量,即为Pa。 为多项式系数,将

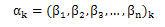

为多项式系数,将 表示为如公式(3)所示的向量形式:

表示为如公式(3)所示的向量形式:

(3)

(3)

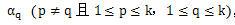

对于向量 以及

以及 (

( ),定义如果其中

),定义如果其中 ,则

,则 同构算法,否则

同构算法,否则 异构算法。对所有的异构算法进行等价类划分得到m个集合

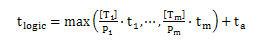

异构算法。对所有的异构算法进行等价类划分得到m个集合 。如图2所示,在用FPGA实现时,对m个异构算法采用并行实现方式。对于同构算法,在各异构结构中实现多个同构的计算晶格来提高同构算法的并行处理能力。若用[Tm]表示集合Tm中元素的数量,用

。如图2所示,在用FPGA实现时,对m个异构算法采用并行实现方式。对于同构算法,在各异构结构中实现多个同构的计算晶格来提高同构算法的并行处理能力。若用[Tm]表示集合Tm中元素的数量,用 表示各异构结构中同构结构的实现数量,用

表示各异构结构中同构结构的实现数量,用 表示每一种同构计算晶格计算一次的时间,用ta表示分配k个计算序列

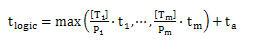

表示每一种同构计算晶格计算一次的时间,用ta表示分配k个计算序列 所消耗的时间,那么整个计算过程所需时间tlogic如公式(4)所示:

所消耗的时间,那么整个计算过程所需时间tlogic如公式(4)所示:

(4)

(4)

(2)可配置性与可扩展性设计

为了便于用户自定义计算规则和业务扩展,从设计架构上采用读入配置文件的方式并且提供扩展空间,实现配置性和扩展性。

可配置性:为用户设计图形化的配置界面软件,当软件接受用户计算请求后会自动生成相应的配置文件,来配置FPGA中的配置寄存器,实现不同要求不同需求、不同用途的运算。

可扩展性:在系统设计中,预留新合约扩展空间,以哈希表等数据结构存储运算。运算过程中,行情数据包到来时,FPGA会通过哈希函数查找哈希表,确定数据的有效性和计算规则,进行逻辑判断进行选择。

(3)基于FPGA的硬件以太网协议跨层解析

在数据分析获取过程中,以太网的协议解析占据了很大的时间比例。如果采用一般的软件解包方法,时间一般延迟包括每一网络层的解包时间和中间数据的传输时间,时间延迟可达毫秒级甚至更高。考虑到降低整个系统的数据传输延迟,进而提升处理性能,提出以下两种解决方案。

1)使用FPGA集成的可配置IP核。FPGA的IP核基于硬件原理实现,在数据传输延迟和网络数据解包能力上都大大优于传统的软件处理过程,而且极大缩短了开发周期,其可靠性,可配置性,通用性都相当出色。适合在项目的中前期作为数据输入的模拟测试。但是具体面向此项目IP核也会有自身的冗余,在MAC层不能进行自定义的协议解析,总的延迟大约在几十微秒至几百微秒。

2)针对本应用设计基于跨层解析的以太网数据分析模型。由于套利计算的数据源的包格式固定,封装简单,而且属于旁路数据,完全可以自行设计针对本应用的专用数据解析功能部分,方案优势和创新点在于在MAC层跨层解析数据以及包过滤,数据接收与解析时间重叠。采用状态机逐层进行包过滤,在有限机器周期内便可获得需要计算的数据,时间延迟可控制在微秒级。

基于FPGA的硬件以太网协议跨层解析能够降低传统软件协议栈的数据包处理固有延迟(可能占据整个延迟的80%以上开销),大大提高数据获取和预处理效率。

(4)高速应用接口设计方案

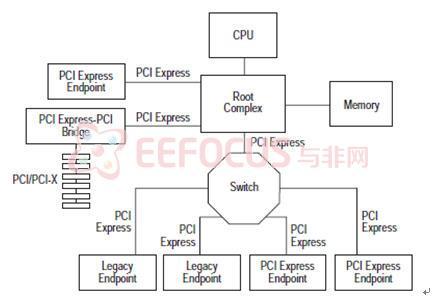

板级数据输出采用PCI-Express接口,PCI-Express接口具有扩展性强、低成本、低延迟、高速率等显著优点。单根链路速率为2.5Gb/s,为了解决本系统的IO瓶颈,在系统输出端拟采用8根链路与PC机通信。那么理论上速度可达到20Gb/s,能够满足系统的速度要求,同时也可以满足系统升级后的速率要求。PCI-Express与PC机连接方式由图8所示,可见PCI-Express的扩展性极强。

图8 PCI-Express拓扑图

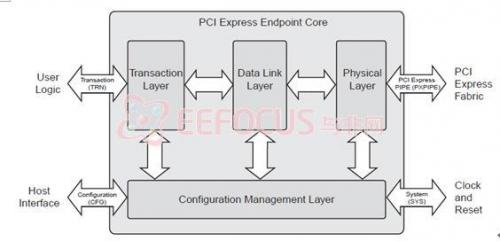

在本系统中主要采用单点的PCI-Express Endpoint与PC机通信,PCI-Express Endpoint功能结构与接口如图9所示,数据主要依次通过Transaction Layer、Data Link LayerPhysical Layer三层传输到另一端。用户可以通过Configuration Interface对PCI-Express进行配置。

图9 PCI-Express

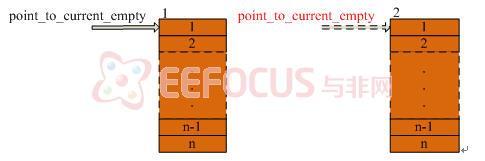

在数据传输密集时,可以配置PCI-Express为突发传输模式,这样,只需经过起始的握手后,便可快速的进行数据传输。如图10所示,在PC机端拟采用乒乓数据缓冲池作为PCI-Express的数据接收缓冲区,当其中一个缓冲区满时,会产生DMA中断通知PC机操作系统,PC机即可对数据进行处理。这种乒乓缓冲池可以在突破PC机处理速度与本系统传输速度不一致的IO瓶颈的同时,减少本系统的IO传输延迟等待。

图10 PC端PCI-Express乒乓数据缓冲池

4.2关键技术与创新点

(1)基于FPGA的实时金融指数并行分析技术

基于FPGA的硬件跨层协议解析与包过滤技术,在接收缓冲网络数据包的同时完成期货套利信息提取,大大降低软件协议栈数据包解析的固有延迟。

行情驱动的专用异构与同构计算单元的协同计算模型,充分挖掘信息计算的并行性,并具有可扩展性和可配置性。

灵活高速的套利合约发布应用接口技术,有效保证信息发布的实时性。

实时金融指数 并行计算 FPGA PCI-Express 突发传输模式 相关文章:

- 可编程图形芯片进入并行计算领域(06-06)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)