CISC处理器调试系统的设计实现,详细软硬件架构、流程、代码

- 前言

随着嵌入式的不断发展,在各个领域的应用越来越广泛,由于嵌入式系统的专用性很强,所以针对不同的应用的嵌入式软件的开发在嵌入式系统开发中所占的比重越来越大。嵌入式系统的开发主要包括两个部分硬件设计和软件设计。软件设计的步骤主要有源码编辑、源码编译、嵌入式操作系统的配置、程序下载和调试。由于嵌入式系统的资源有限不可能在嵌入式系统的硬件平台上集成自身的软件开发环境,所以嵌入式的软件开发的通常采用交叉编译和调试的方式。调试是保证程序质量的重要手段之一,可以验证程序是否满足预期的要求和检查程序存在的bug。交叉的开发方式采用宿主机和目标机的结构。宿主机一般采用PC机,将嵌入式系统的软件开发环境配置在PC机上。宿主机和目标机之间通过串口、并口和网线等建立连接,不仅仅是物理连接还有逻辑连接。在交叉开发过程中宿主机和目标机通过这种连接进行交互,完成目标程序的编译下载和调试。

嵌入式系统的开发主要针对硬件系统中的微处理器的嵌入式软件的开发,嵌入式系统的软件调试也是针对微处理器的调试。现在微电子技术飞速发展,处理器生产工艺也不断提高,微处理器芯片的集成度更高、运行频率更高,所以对调试的要求更高。单单采用PC机上的软件调试器和软件调试代理已经很难适应这些新的变化,将调试功能转移到硬件部分为嵌入式软件的开发提供更好的保障和支持,实现成本也比较低。微处理器芯片中集成支持调试的硬件逻辑已经逐渐成为趋势。

在板级的测试和调试领域,为了更好的支持对电路物理节点的访问,JTAG标准已经被很多芯片生产厂商所采用。JTAG标准最早的提出是为了检测印刷电路板的元件焊接问题,通过在电路中引入边界扫描单元所组成的边界扫描链来完成对电路节点的访问。现在JTAG标准也被应用于嵌入式软件的调试过程中,用于与硬件调试逻辑交互提供通用的调试接口。

- 总体方案设计

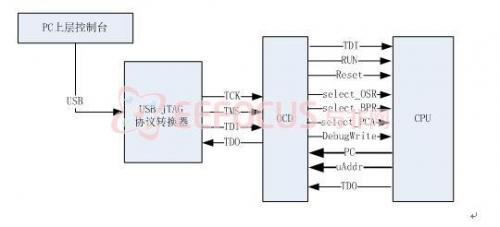

图1 系统结构框图

整个调试系统分为四部分PC机上层控制台,USB-JTAG协议转换器,片上调试器OCD(On Chip Debugger)以及调试的目标处理器CPU。

- 系统硬件

- USB传输

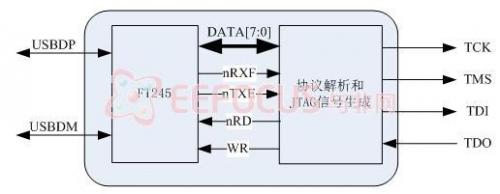

USB是以串行传输的方式传输数据,首先使用FTDI公司的USB串并转换芯片FT245R将USB串行数据转换为并行数据,然后USB-JTAG协议转换器根据接收到的数据按照JTAG协议输出TAP信号。USB-JTAG协议转换器的结构如图1所示。

图 1 协议转换器的结构

USB-JTAG协议转换器与FT245R之间除了有8位的数据Data[7:0]的传输,还有四个握手信号,分别是nRXF、nTXE、nRD和WR,如图1所示。nRXF是读FIFO_TX允许信号,nTXE是写FIFO_RX允许信号,还有读FIFO_TX信号nRD和写FIFO_RX信号WR。当nRXF为低电平时说明FIFO_TX不为空,USB-JTAG协议转换器可以从中读出数据,此时USB-JTAG协议转换器可以通过发送nRD信号从FIFO_TX读取数据;同样当nTXE信号有效的时候表明FIFO_RX还有空间,此时USB-JTAG协议转换器可以使WR信号有效往FIFO_RX中写入数据。USB-JTAG协议转换器对FIFO_TX和FIFO_RX的读写操作都是以字节为单位。

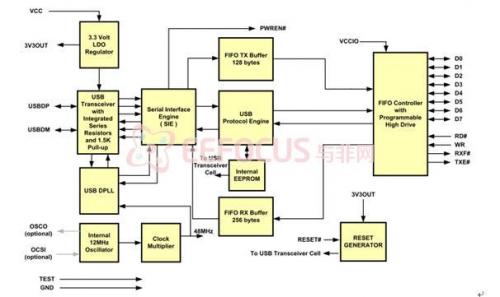

FT245R内部有两个FIFO分别为FIFO TX Buffer和FIFO RX Buffer,FIFO TX Buffer负责存放接收从PC机发送来的数据,FIFO RX Buffer负责接收从USB-JTAG协议转换器发送来的数据,为了区分称之为FIFO_TX和FIFO_RX。FT245R芯片的内部结构如图2所示。

图2 FT245R芯片的内部结构

- SPARTAN-3E开发板

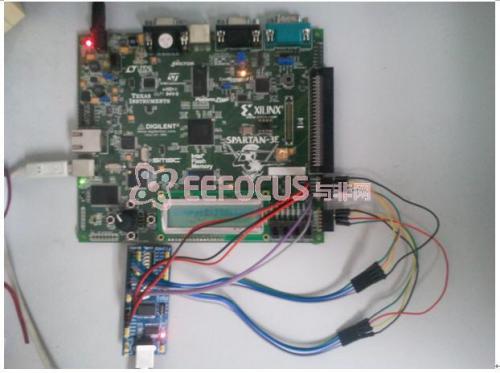

采用xilinx的SPARTAN-3E开发板,将目标处理器与片上调试器的硬件逻辑还有协议转换器中的JTAG信号的生成功能都集成到该开发板的FPGA上。系统如图3所示。

图3

- 片上调试器结构

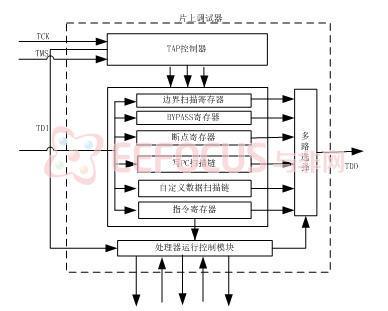

图4 片上调试器结构

TAP控制器掌管JTAG协议的状态机,控制OCD与USB-JTAG协议转换器之间的数据和指令的移入移出。TAP(Test Access Port)包含四个引脚用来控制指定的操作。这四个引脚分别为TMS,TCK,TDI,TDO。TAP控制器内部采用标准的JTAG协议状态机来控制TAP的数据通路,包括指令寄存器扫描链和数据寄存器扫描链的选择以及扫描链数据的传输。

寄存器包括边界扫描寄存器、BYPASS寄存器、断点寄存器和指令寄存器。边界扫描寄存器在此处是为读取处理器输入输出引脚预留的扩展寄存器;BYPASS寄存器是位宽为1的寄存器,当在多个器件或模块串联的时候用该寄存器来旁路当前器件或模块;指令寄存器主要用来存放对CPU进行调试的相应调试指令。

扫描链包括写PC扫描链和自定义数据扫描链。写PC扫描链是为了写入PC值而设计的扫描链,而通过自定义数据扫描链可以读出处理器内部的状态和数据。

处理器运行控制模块是片上调试器的核心部件,负责调试指令的译码以及读CPU寄

CISC处理器 调试系统 片上调试器 Spartan-3E 协议转换器 相关文章:

- TD-LTE多模基带平台ARM子系统的运行流程控制和异常定位分析(08-24)

- 基于GAL的BDM调试系统设计(06-05)

- 应用调试-----自制系统调用、编写进程查看器(11-21)

- 嵌入式软件跟踪信息嵌套缓存机制和解析机制的设计(10-18)

- GDB RSP协议与USB通信在嵌入式调试系统中的应用(11-14)

- ARM体系中调试系统概述(11-22)