CISC处理器调试系统的设计实现,详细软硬件架构、流程、代码

时间:06-04

来源:互联网

点击:

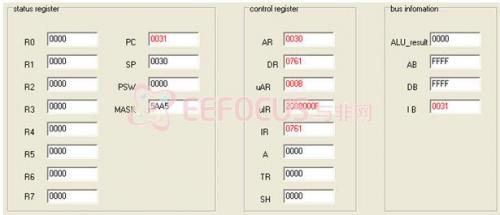

点值已经正确的写入。然后运行处理器,由于当处理器运行停止时读取处理器内部寄存器状态,结果返回如图6。其中UAR显示现在处理器停止的微指令的位置,读出的其他寄存器值也是运行到当前微指令断点的值。

图6 微指令断点返回结果

- 连续运行和停止

连续运行是处理器运行在正常情况下,此时并不需要片上调试器的干涉,至于停止运行则是让处理器运行完当前机器指令则停止。由于在内存中存储的程序很短,而处理器的运行速度很快,所以在发送完连续运行调试指令,可以马上执行停止运行调试指令内存中的测试指令已执行完成了,所以在停止运行指令之后再通过PC机控制台来读取处理器内部寄存器的值就不会改变了。如7、8两张截图是停止运行指令之后两次读取数据的结果,可以看出结果不再变化,证明停止调试指令正确实现。

图7 第一次读结果

图8 第二次读结果

- 总结

在嵌入式系统的开发过程中,调试是不可或缺的一环。一个好的调试器可以大大的提高系统开发的效率,缩短推出产品的时间,同时也提高了系统的可靠性。

本文设计了一个基于JTAG协议的片上调试器,该片上调试器实现了微指令和机器指令的单步、断点以及读取处理器内部寄存器和写入PC、处理器复位等常用调试功能。构建扫描链时采用独立的扫描通路不对处理器本身寄存器做任何修改,这样在保证实现调试功能的同时还最大程度的保护了处理器数据通路的独立性,将对处理器的侵入性降到一个比较低的水平。

CISC处理器 调试系统 片上调试器 Spartan-3E 协议转换器 相关文章:

- TD-LTE多模基带平台ARM子系统的运行流程控制和异常定位分析(08-24)

- 基于GAL的BDM调试系统设计(06-05)

- 应用调试-----自制系统调用、编写进程查看器(11-21)

- 嵌入式软件跟踪信息嵌套缓存机制和解析机制的设计(10-18)

- GDB RSP协议与USB通信在嵌入式调试系统中的应用(11-14)

- ARM体系中调试系统概述(11-22)