基于FPGA的实时金融指数行情并行计算

高和现场可配置等特点,所以在短短的几十年里,现场可编程逻辑嵌入式系统设计技术已经成为信息产业最热门的技术之一,应用范围遍及金融、航空航天、医疗、网络通讯、安防、汽车电子、工业等多个热门领域。在特定领域与传统PC机相比,FPGA能够将处理速度提高几个数量级。

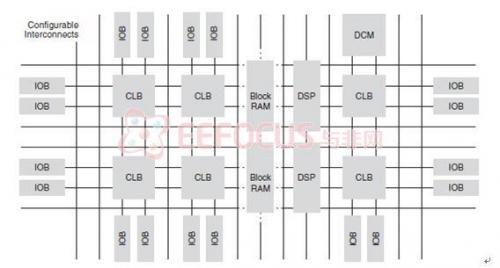

如图1所示,FPGA主要由逻辑控制块(CLB)、输入输出控制块(IOB)和内部连线三大部分组成,同时芯片内部集成块状存储器(BlockRAM)以及数字信号处理单元DSP以满足高速数据处理应用环境的需求。

图1 FPGA内部原理图

三、项目内容与研究目标

3.1研究内容

- 实时金融指数行情计算模型与并行调度策略

研究实时金融指数(本计划书以股票ETF50为例)股票推导的计算模型与计算方法,根据数据计算类型的特点设计专用硬件处理单元的结构模型;

研究有限计算资源条件下的行情数据缓存与并行调度策略,研究硬件计算资源划分与共享技术;

研究透明数据接口技术,包括输入端旁路高速数据获取技术与实现方法以及输出端的应用接口技术。

- 基于FPGA的并行加速技术

研究基于FPGA的硬件千兆以太网数据获取技术,实现完全硬件的TCP/IP协议栈解析和数据包过滤;

研究行情驱动的大规模专用套利数据处理单元结构、数据缓存与并行分发机制以及数据流水调度算法。

研究面向同构计算单元(同种计算模型)和异构计算单元(异种推导模型)协同的FPGA资源划分技术,对资源进行优化配置,在有限计算资源条件下获得最高的并行加速性价比。

实时金融指数行情的可配置与可扩展技术,充分考虑FPGA专用逻辑特点提供计算模型的配置与合约推导的扩展方案。

研究实时金融指数行情数据的高速分发及应用接口技术,采用高速传输总线结构实现实时金融指数行情数据的提取和管理。

3.2研究目标

(1)实现实时金融指数的大规模硬件并行加速,将数据处理的性能提升3-4个数量级。给出数据获取、数据分析、数据发布的总时间开销的最大加速比以及资源扩展性价比分析。

(2)实现基于FPGA的千兆以太网数据获取与硬件协议栈解析,突破软件协议栈解析的性能瓶颈;设计并实现行情驱动的硬件数据缓存、数据分发、并行调度与管理;实现基于FPGA的异构与同构计算单元相结合的大规模数据并行处理,实现多粒度流水控制和资源复用。

(3)提出加速平台集成方法,设计集成平台的芯片级与板级的动态扩展结构;给出FPGA并行处理性能随计算模型复杂度、股票信息数量、数据传输速率变化的评测分析报告,以及股票交易系统业务类型的硬件加速适应性分析报告。

四、实施方案与技术路线

本项目实施首先分别采用FPGA设计实时金融指数行情的并行处理结构,并通过测试数据和简化计算模型验证系统的可用性,对比分析硬件并行的加速比并给出随输入条件变化的性能提升分析,然后设计基于FPGA加速平台的系统结构和核心调度策略。

本项目的主要目标是降低“实时金融指数行情”的计算和传输延迟,达到实时的指标数据分析,因此性能评价是对数据获取时间Tg、数据处理时间Ta、数据发布时间Ts的总时间Tt的评价公式(1)所示:

(1)

(1)

其中,基于FPGA的设计方案除采用并行结构降低Ta,还实现硬件的协议栈解析,从而大大降低Tg,同时也采用硬核方式降低Ts的延迟;而FPGA在内存交换的优势将有效降低Ts。

4.1基于FPGA的并行加速技术方案

(1)基于FPGA的并行加速总体结构

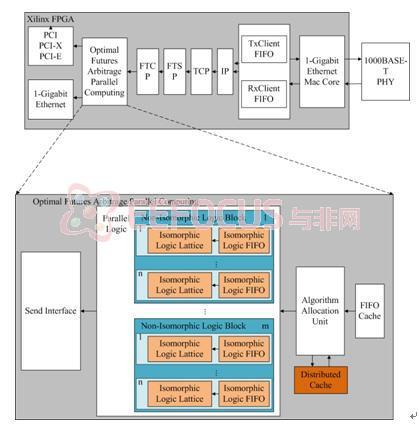

图3-1为系统结构图,主要由数据接收模块、股票信息并行处理模块、数据发送模块组成。数据接收模块主要负责协议包的跨层解析以及包过滤。股票信息并行处理模块是整个系统的算法核心,采用高速并行方式分析股票信息,计算相关指数,并通过数据发送模块快速发布。在股票信息并行处理模块中,算法定向单元负责调度下层的异构逻辑块,异构逻辑块通过同构逻辑晶格完成最基础的数据计算。在股票信息并行处理模块中,将所有的数据存储于FPGA内部的分布式RAM中,突破了IO传输的瓶颈。

图7 FPGA计算系统结构图

对于数据计算,每一种股票指数都有自己的指数计算的方法(本计划书以上证50指数为例):

上证 50 指数采用派许加权方法,按照样本股的调整股本数为权数进行加权计算。计

算公式为:

Ip = Pa / base * 1000 (1)

Ip:报告期指数 Pa:报告期成份股的调整市值 base:基 期

其中,Pa = Σ(Pi× St) (2)

Pi:市价 St:调整股数。

调整股本数采用分级靠档的方法对成份股股本进行调整。

上证50 指数的分级靠档方

法如下表所示。

流通比例(%) ≤10 (10,20] (20,30] (30,40] (40,50] (50,60] (60,70] (70,80] >80

加权比例(%) 流通比例 20

实时金融指数 并行计算 FPGA PCI-Express 突发传输模式 相关文章:

- 可编程图形芯片进入并行计算领域(06-06)

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)