基于FPGA的多路CameraLink数据的WDM光传输

一、系统总体介绍

本系统是基于FPGA的多路CameraLink数据的单光纤传输设计,由于FPGA的开发成本低廉,升级方便所以成为该系统设计的选择。

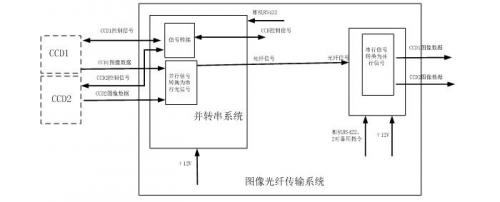

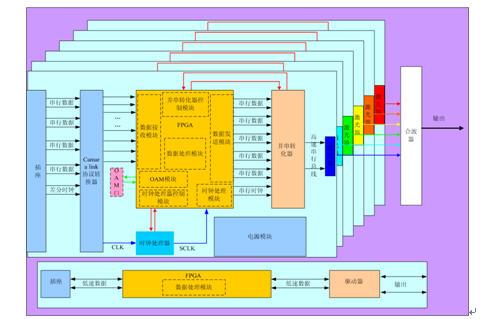

图像光纤传输系统主要由并转串系统和串转并系统组成,系统组成的框图如图1.1所示。

并转串系统将两台CCD的并行图像数据转换为串行光信号,经光纤传输后发给串转并系统,串转并系统将光信号再恢复成两台CCD的并行图像数据。光纤上传输的图像数据速率在1.4G-2.8G内可调。

图1.1系统组成的框图

二、系统工作原理和组成

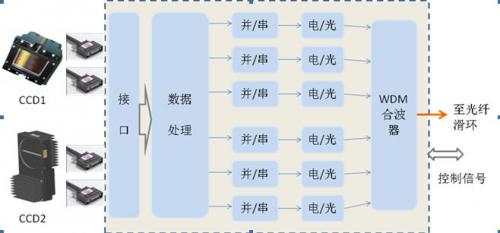

基于成本和实现难度的考虑,主要的工作原理是采用电路并串变换+光波分复用(WDM)的方式实现超大容量数据合成,完成数据通过一根光纤传输的功能。也就是先将每一组Camera link 数据进行并串变化,形成一路串行信号,之后通过WDM技术将各路串行信号的各个波长通过光路合成到一根光纤当中,经过传输后(主要是经过光纤),在接收端还原成各个波长,经过处理后恢复出原始信号。

系统基本组成如下图所示。两个可以full配置的CCD摄像头分别通过两条26芯标准电缆将图像数据传给本系统。每个Camera Link数据组X、Y和Z分别通过接口进入系统,并完成并串转换、电光转换、合波等,最后统一到一根光纤。经过光纤传输后,再由接收部分经过分波器、光电转换、串并变换和输出接口后,恢复为同从CCD接收到的原始数据完全相同的格式,再通过四条26芯标准电缆将数据输出给下级处理设备。

图2.1 系统组成框图

三、实现方案

3.1总体思路

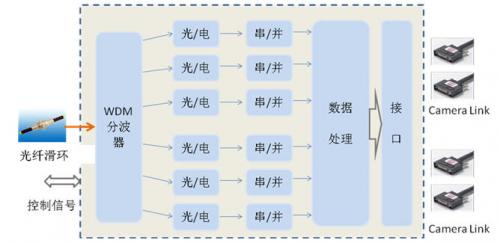

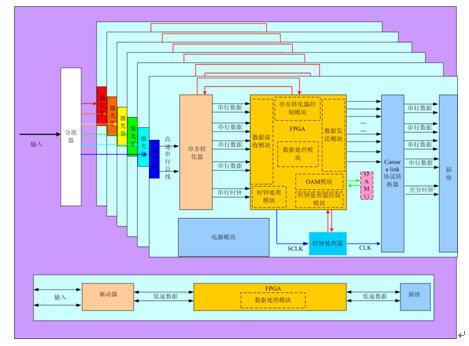

图3.1 系统方案框图

系统采用电路串并变换+光波分复用(WDM)的方式实现超大容量数据合成的方式,完成数据通过一根光纤传输。系统的构成如图3.1所示。

系统分为发送部分单元和接收部分单元。发送部分单元和接受部分单元又各分为高速部分模块和低速部分模块两部分。高速部分模块独立完成数据的串化、解串化工作;低速部分模块完成相关数据和控制信号的处理。

发送部分单元高速电路完成六路Camera link 总线(两个CCD full配置的数据量)的串化,把每一路camera link 总线的数据串化后,送入激光器变成光信号,再用波分复用的形式通过一根光纤传送出去。发送部分总体框图如图3.2所示。

图3.2 发送总体框图

接收部分单元高速电路完成六路camera link 总线 (两个 CCD full配置的数据量)的解串工作,首先通过波分解复用系统分出每一路camera link 总线的数据,然后再把每一路串化的camera link 数据解串,恢复成标准的并行信号。接收部分总体框图如图3.3所示。

图3.3 接收总体框图

在系统地评估产品的复杂性和可靠性的需求后,我们决定选用Xilinx Spartan3E系列产品作为FPGA核心模块的首选器件。Xilinx 3E系列产品价格较低,功能全面,是世界上畅销的 FPGA。

3.2发送部分单元

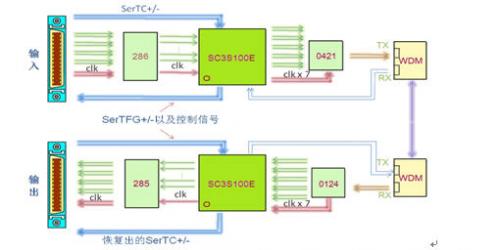

发送部分单元高速电路完成六路Camera link 总线(两个CCD full配置的数据量)的串化,把每一路camera link总线的数据串化后,送入激光器变成光信号,再用波分复用的形式通过一根光纤传送出去,发送单元电路模块整体框图如图3.4所示。

图3.4 发送单元电路模块整体框图

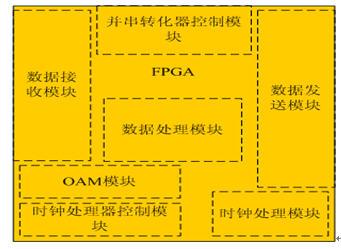

发送单元包含如下几个模块,如图3.5所示:

发送单元数据接收模块:完成正确接收来自Camera link 协议转化器的数据的功能;

发送单元数据处理模块:完成发送数据的核心处理功能;

发送单元数据发送模块:完成正确将合成的数据以和Serdes匹配的形式发送到serdes的功能;

发送单元并串转化器控制模块:完成对并串转化器的OAM功能;

发送单元时钟处理模块:实用内部的时钟部件完成时钟的相应处理,比如分频、倍频、相位调整等;

发送单元时钟处理器控制模块:完成对时钟处理器的OAM的功能;

发送单元OAM模块:和上层控制管理器配合,完成发送系统的OAM工作。

图3.5 发送单元模块划分

下面详细介绍发送部分单元模块具体功能及实现:

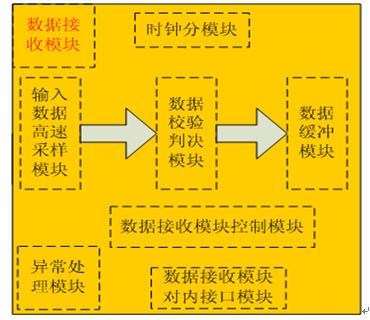

发送单元数据接收模块完成数据的正确接收、判决和缓冲的功能。模块内部逻辑框图如图3.6所示。包括输入数据高速采样模块、数据校验判决模块、数据缓冲模块、数据接收模块控制模块、数据接收模块对内接口模块、异常处理模块和时钟分模块。

图3.6 发送单元数据接收模块内部逻辑框图

数据缓冲模块:对数据校验判决模块产生的数据进行缓冲,提高数据的可靠性和系统的安全性,出现溢出或者空闲的时候上报相关信息给数据接收模块控制模块便于OAM。

异常处理模块:提供不可预测的异常处理,比如复位等,以提高系统的可靠性和稳定性。

时钟分模块:提供本模块需要的时钟。异常处理模块不需要时钟;数据接收模块对内接口模块时钟为OAM模块工作时钟;数据接收模块控制模块为异

CameraLink 多路 FPGA WDM 光传输 相关文章:

- 基于FPGA的多路视频通道控制 (01-09)

- 多路测量信号扩频传输的DSP系统(03-18)

- 基于DSP和CPLD技术的多路ADC系统的设计方案(05-19)

- 多路交流异步采样及DSP软件校准技术(10-13)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 基于FPGA的脉冲重复频率(PRF)跟踪器的设计(06-05)