多路交流异步采样及DSP软件校准技术

本文介绍了一种在DSP平台下对多路交流信号采样时采用的一种异步采样方法。

引言

在对电力线路的电压和电流进行测量时,为使测量值具有较高的精度,一般都采用交流采样技术。目前,比较常用的交流采样方法是:在交流信号的一个周期内,等间隔采样N点数据,然后利用傅立叶变换,计算出基波及一些谐波的有效值,为衡量供电质量通常还要求计算出各信号的相位。但由于同一测量装置要同时对很多路电压和电流量进行采样,而采样所用的A/D的输入又有限,不可能对电压和电流量同时进行采样,所以,一般将所有的交流通过多路开关的切换依次送入A/D进行采样。由于采用的是异步采样,所以同一个线路中的A、B、C三相之间的相位就会产生误差,所测出的同一个交流量的电压值和电流值之间的相位也会产生误差,如果不对相位采取一定的处理措施,就不能有效的提高计算值的精度。

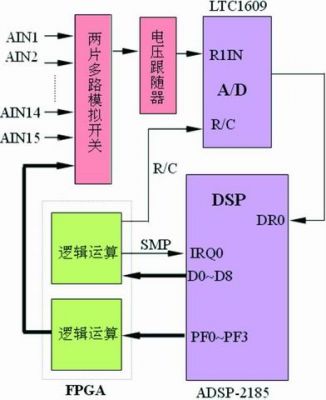

硬件系统

硬件系统的示意图如图1所示。外部输入的电压电流经过电压互感器或电流互感器,经过信号调理,变换成小电压信号,把这些小电压信号经过滤波、放大处理之后送入模拟多路开关。接入多路开关的信号AIN1、AIN2、…AIN15的切换由DSP通过FPGA来控制。多路开关的输出接电压跟随器,以降低信号源的输出阻抗,保证得到较高的采集精度。经A/D转换完成后的数据由DSP芯片进行采集处理。

A/D可以选用Linear公司的16位双极性高精度模数转换器LTC1609。

如果进行N点傅立叶变换,应该在一个周期内等间隔均匀采样N个点。但如果以固定的时间间隔进行采样,当电网中交流信号频率偏离50Hz时,所采集到的N个点就不一定恰好为一个周期的数据。所以,在本系统中,DSP实时监测交流信号周期的变化,根据当前最新的周期值TAC计算出两个采集点之间的间隔时间为:

TSMP=TAC/N

DSP将TSMP送给FPGA,FPGA经过运算,产生两个信号:一个是采样命令信号SMP、另一个是启动A/D转换信号R/C,这两个信号都是低电平有效。图2是用MAX-PLUS II软件仿真出的SMP与R/C信号的波形关系。

图2 SMP和R/C的波形示意图

当SMP信号到来时,表示新一轮采样的开始。SMP信号后紧跟15个R/C信号,依次负责对15路输入信号的A/D转换。所以每一轮采样可以对15路信号各采集一个点。每个点的数据经过64阶有限冲激响应滤波器滤除高次谐波之后存储在缓冲区内。

当A/D采用内部时钟模式时,先将A/D的片选/CS置为低电平,在R/C信号的下降沿,A/D将当前输入的信号转换为保持状态,开始进行A/D转换,同时A/D开始将上一次的转换结果向DSP发送。转换开始后R/C必须在1ms内跳回至高电平,以确保输出结果不会发生错误。本系统中,R/C信号的低电平持续0.5ms。两个R/C信号的下降沿之间的间隔TRC设置为12ms,以保证A/D启动下一路转换时当前的转换能够结束,以及上一次转换后的结果送入DSP。

校准

经过N个SMP信号之后,DSP就为15路信号各收集了一个周波共点的数据。对点数据进行快速傅立叶变换,得到各路信号的基波和若干次谐波所对应的频域值。从而可以求出有效值、相角等各个量。但实际上由于信号的幅度和相位经过变换、滤波、放大、采样、量化后处理时都要偏离理论值,所以,对于FFT运算的结果要进行校准处理。

可以用一个标准三相交流电源,将它的输出电压调整为电压100V、输出电流调整为5A、频率为50Hz、ABC三相各相差120度,然后将电压电流信号接入系统对应的输入端,通过上层软件向DSP发送校准命令,开始计算幅度和相位的校准参数。

幅度校准

如果有效值为100V、频率为50Hz的电压信号经过A/D转换后的数值大约在P左右,那么,我们就可以用P作为一个标度,用它来代表100V。同样,我们可以Q代表有效值为5A、频率为50Hz的电流。

在校准过程中,假定得到的m路电压的有效值的数字量为=[V1,V2,...Vm],得到的电流的数字量为=[I1,I2,...,I15-m],则我们把它们通过一个电压校正系数=diag[a1,a2,...,am]和电流校正系数=diag[b1,b2,...,b15-m]将其校正到标度上去。即有如下公式:

可求得

ai=P/Vi,b=Q/Ij 其中i=1,2,…,m;j=1,2,…,15-m

在系统正常工作时,将得到的信号的幅度有效值乘以校准系数可以得到比较精确的数值。

相位校准

交流电的相位关系是反映供电质量的比较重要的参数。相位校准从两个方面进行:一方面要补偿多个信号由于异步采样造成的相位偏差;另一方面要校准信号调理过程中造成的相位偏移。

如图3所示,假定在t时刻对一个信号采样的结果如(a)所示,但如果延迟到t+Dt采样的话,其结果如(b)所示,(b)与(c)的相位是一样的。通过对比可知,(c)的相位比(a)的相位超前,即,

- 基于FPGA的多路视频通道控制 (01-09)

- 多路测量信号扩频传输的DSP系统(03-18)

- 基于DSP和CPLD技术的多路ADC系统的设计方案(05-19)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 基于FPGA的脉冲重复频率(PRF)跟踪器的设计(06-05)

- 多时钟FPGA设计策略阐述(06-05)