FPGA应用在列车闭塞控制系统提高系统集成与稳定性

列车运行控制系统主要是以对列车运行方向,运行间隔和运行速度进行控制,使列车能够安全运行且提高运行效率,列车运行控制系统地面设备和车站联锁设备主要实现联锁控制功能,并生成列车控制所需基础数据,通过车地信息传输通道将地面控制信息传送给列车,经列车运行控制设备进行处理后,生成列车速度控制曲线,监控列车安全,高速运行,列车控制系统以固定闭塞分区为基础,分为分级速度列车运行控制系统设备,由地面设备及车载设备两部分组成。地面设备由轨道电路,列车运行控制中心和维护系统三大部分构成。

车载部分由双重结构组成安全型计算机接收地面传输的有关信息,计算并生成速度控制曲线,速度控制与列车速度比较,对超速列车实行制动,列车运行控制中心对轨道电路参数计算形成线路参数,前方目标距离,允许行车速度等不同信息,经调制及钢轨连续传输发给列车。维护系统对地面设备实行远程诊断与监测管理。

列车的开环控制变为闭环控制,实现了以车载设备为主的行车方式,通信信号一体化是现代铁路重要发展趋势,故障安全为最重要的技术条件;列控系统通常由地面控制中心或无线闭塞电路地面信号设备,车地传输设备和车载速度控制设备组成,用于控制列车运行速度保证行车安全和提高运输能力的控制系统,列车的车载系统会适时将车载滤波器转换到正确的频率范围上从而实现列车只接收正确的载波的数据帧,相应的滤波器以电路选择方式实现以准备好对即将进入区段的采用预定8种载频之一进行调制的安全数据帧接收和译码。

闭塞系统由轨旁盒与室内控制组成,轨旁盒是连接电气与室内设备的中间设备,是轨道电路室外发送接收设备,系统核心是系统运行控制部分;其关键部分是放大滤波板,其实是把发生器发来的调制音频电压提升到所需要的电平,并通过带通滤波器送到轨道馈入点,每种频率都有自己的专用的放大滤波板。

发送滤波器输入的信息:

FSK信号:由发送板送人,经调制FSK方波信号,发送滤波器输出的信息:

FSK正弦波信号,经过电桥,送入方向转换板,此信号是已经放大和滤去高次谐波的相应频率的正弦波。

模拟前端硬件

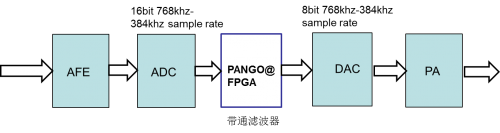

信号接收端由跟随器,运算放大器以及ADC组成。将接收到的移频信号进行放大整形送入ADC进行模数转换,将数字信号送至下级的FPGA实现的高精度FIR滤波器。如图1-1所示:

图1-1.FPGA滤波器实现方法

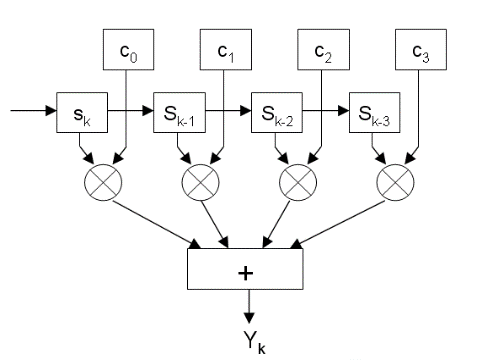

由于带通滤波器的指标比较高,若要实现相应的指标对于FIR滤波器的阶数要求较高需要200阶以上,如果采用传统的滤波器实现方法,则需要耗费大量的逻辑资源和MAC乘累加单元,DFF寄存器需要几K左右。如图1-2所示,每一阶则需要14bit的DFF资源乘上相应的阶数会占用很大的逻辑资源,MAC也需要与阶数相同,硬件是无法满足的。

图1-2.传统滤波器实现方法

考虑到同创国芯芯片中已有的资源包括DRM嵌入式存储器、APM MAC乘累加单元和CLM逻辑单元,以及芯片的性能。采用如图1-1的实现方法,则可以节省大量的逻辑单元和MAC乘累加器。

通过FPGA实现DSP算法可以极大提高系统性能和降低设计复杂度,以数字FIR 为例,通过优化设计DSP执行乘-累加MAC操作,顺序执行N个MAC中每一个操作,因此可达到最大运行速度大约为Fclock/NHz,其中Fclock为DSP最高时钟频率,而使用FPGA可以全并行地实现滤波器,其中并行执行N个MAC操作(而不是顺序执行)对于同样的Fclock滤波器执行速度可以提高N倍。大多数DSP提供32位精度累加器用于保存MAC操作结果,而对于FPGA,理论上可以实现任意精度的操作,可以在10-16位宽度范围内实现大部分滤波器功能。

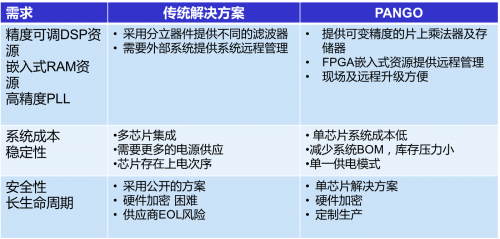

使用FPGA在闭塞列控系统的优势非常明显:

同创国芯TITAN@系列可编程逻辑器件采用了完全自主产权的体系结构和主流的40nm工艺。 PG系列产品包含创新的可配置逻辑单元(CLM)、专用存储单元(DRM)、算术处理单元(APM)、多功能高性能I/O以及丰富的片上时钟资源等模块,为客户提供高性能,大容量,差异化应用的FPGA产品。 我们创新的提出具有自主知识产权的逻辑架构“CLM”(Configurable Logic Module, 可配置逻辑模块)-- 是TIIAN系列器件的基本逻辑单元,主要是由多功能LUT5,寄存器以及扩展功能选择器等组成,CLM集成了专用电路实现4:1多路选择器功能和快速算术进位逻辑;扩展功能选择器主要用于实现宽位查找表和输出选择功能. 这样客户在实现同级间逻辑级联可以得到更高的速度;此外相邻的两个CLM之间还有一条基于LUT7的专用级联链,用于组合生成LUT8。CLM的使用可通过关联的综合工具(Synplify Pro)和同创国芯电子有限公司的软件Fabric C

- 在采用FPGA设计DSP系统中仿真的重要性 (06-21)

- 基于 DSP Builder的FIR滤波器的设计与实现(06-21)

- 基于FPGA的快速并行FFT及其在空间太阳望远镜图像锁定系统中的应用(06-21)

- 3DES算法的FPGA高速实现(06-21)

- 用FPGA实现FFT算法(06-21)

- FPGA的DSP性能揭秘(06-16)