基于FPGA的多路CameraLink数据的WDM光传输

模块:完成对时钟处理器的核心控制工作,包括对时钟处理器的关键数据的监控、关键设置的确认等工作,是模块的核心子模块。

IIC数据总线读写时序成型模块:负责对时钟处理器的读写操作,要求模块完全满足IIC数据总线时序的要求,能准确完成读写操作,并增加相应的防误操作功能,确保读写的正确性。

初始化配置模块:保存时钟处理器初始化数据,此数据为默认正常工作的数据,不可更改,如果需要更改则上电配置完成后由OAM模块发起,经由核心控制模块对时钟处理器进行操作。

发送单元OAM模块

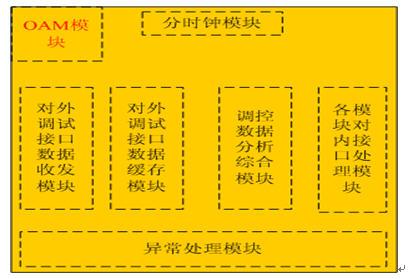

本模块通过内部接口和发送接收模块其他系统模块进行通信和交流,对其他模块进行控制和管理;同时,本模块通过OAM模块对外接口模块和外部的上层管理控制平台相连,接受外部上层管理控制平台的指令,完成相应的操作并上报相关的信息,这部分设计还需要进行沟通确认后才能正常开始设计。模块内部逻辑框图如图3.12。包括对外接口数据收发模块、 对外接口数据缓冲模块、数据分析综合模块、对内接口模块、时钟分模块、异常处理模块。

图3.12 发送单元OAM模块内部逻辑框图

以下是各个分模块的具体介绍。

对外接口数据收发模块:完成串口时序的成型,正确完成串口的读写操作,保证读写操作的正确性。。

对外接口数据缓冲模块:缓冲来自串口的信息,在内部处理速度比较慢的情况下仍能保证不丢失指令。

数据分析综合模块:对上层管理平台的命令进行解析,分析命令的动作和需要处理的方式,将复杂命令分解为需要哪几个模块完成什么样的操作,下发给各个实体操作模块。同时对各个实体模块上报的信息进行综合和管理,编制成符合上层管理平台需要的回复后回复给上层管理控制平台。

3.3 接收部分单元

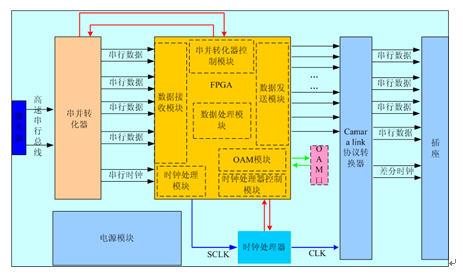

图3.13 接收单元电路模块整体框图

接收部分单元完成六路camera link 总线 (两个 CCD full配置的数据量)的解串工作,先通过波分解复用系统分出每一路camera link 总线的数据,然后再把每一路串化的camera link 数据解串,恢复成标准的并行信号。图3.13是接收单元整体功能框图:

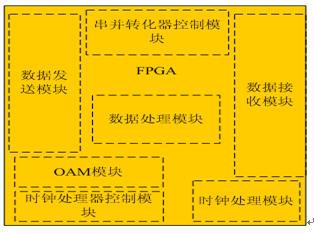

接收单元包含如下几个模块,如图3.14:

接收单元数据接收模块:完成正确接收来自serdes的数据的功能;

接收单元数据处理模块:完成数据的核心处理功能;

接收单元数据发送模块:完成正确将分析出来的数据发送到Camera link协议转化器的功能;

接收单元串并转化器控制模块:完成对串并转化器的OAM功能;

接收单元时钟处理模块:实用内部的时钟部件完成时钟的相应处理,比如分频、倍频、相位调整等;

接收单元时钟处理器控制模块:完成对时钟处理器的OAM的功能;

接收单元OAM模块:和上层控制管理器的配合,完成发送系统的OAM工作。

图3.14 接收单元模块划分

下面详细介绍接收部分单元模块具体功能及实现:

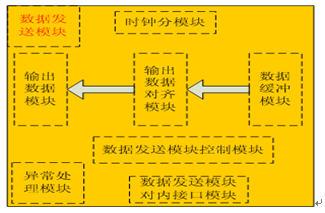

接收单元数据发送模块

接收单元数据发送模块完成数据的缓冲、对齐处理并发送给camera link 协议转化器的功能。模块内部逻辑框图如图3.15。包括数据缓冲模块、数据对齐模块、输出数据模块、数据发送模块控制模块、数据发送模块对内接口模块、异常处理模块和时钟分模块

图3.15接收单元数据发送模块内部逻辑框图

数据缓冲模块:对发送单元数据处理模块产生的数据进行缓冲,提高数据的可靠性和系统的安全性;出现溢出或者空闲的时候上报相关信息给数据发送模块控制模块便于OAM。

数据对齐模块:对数据进行对齐操作,并进行相关的处理,保证发送出去的数据满足camera link 的规范要求。

输出数据模块:进行时序调整,将数据发送到camera link 协议转化器。

控制模块:接收来自接收单元数据发送模块的相关信息,通过数据发送模块对内接口模块和OAM模块进行交互,完成OAM模块对本模块的管理。

对内接口模块:完成数据发送模块控制模块和接收单元OAM模块之间的通信和数据交流。

异常处理模块:提供不可预测的异常处理,比如复位等,以提高系统的可靠性和稳定性。

时钟分模块:提供本模块需要的时钟。

接收单元数据处理模块

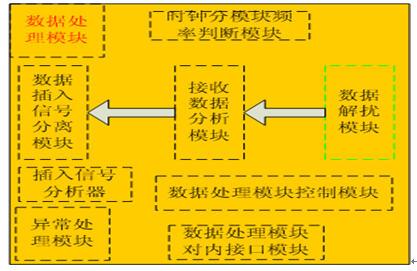

接收单元数据处理模块完成核心的数据接收的功能。模块内部逻辑框图如图3.16所示。包括数据解扰模块、数据分析模块、数据插入信号分离模块、插入信号分析器、数据处理模块控制模块、数据处理模块对内接口模块、时钟分模块、异常处理模块。

图3.16接收单元数据处理模块内部逻辑框图

以下是各个分模块的具体介绍。

数据解扰模块:该模块主要完成解扰过程,保证正确提取数据。

数据分析模块:完成30bit的帧结构的定帧操作,并正确确定出28bit数据信号和相应的定帧信号,并判定数据是否经过double处理。工作状态可以由数据处理模块控制模块进行相关

CameraLink 多路 FPGA WDM 光传输 相关文章:

- 基于FPGA的多路视频通道控制 (01-09)

- 多路测量信号扩频传输的DSP系统(03-18)

- 基于DSP和CPLD技术的多路ADC系统的设计方案(05-19)

- 多路交流异步采样及DSP软件校准技术(10-13)

- 基于FPGA的高速多路视频数据采集系统设计(06-05)

- 基于FPGA的脉冲重复频率(PRF)跟踪器的设计(06-05)