基于ADF4360-0的微波扫频信号发生器设计

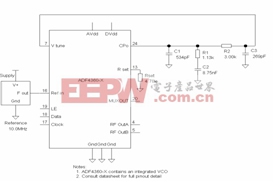

ock time)之间进行取舍。在较小的回路带宽情况下,杂散也较小,但是锁定时间较慢。在较大的回路带宽情况下,锁定时间较快但杂散较高。事实上,在设计时,可以利用ADI公司提供的ADIsimPLL工具计算出三阶环路滤波器的元件参数如下:R1=1.13kΩ,C1=534pF,C2=8.75nF,C3=269pF,R2=3kΩ。

3.3 电路的PCB设计

电路的PCB设计同样也很重要,要注意以下几点:

① 为了便于焊接,画芯片封装时,芯片引脚的焊盘要比实际尺寸长0.5mm,宽0.05mm;

② 在射频信号线、焊盘和芯片周围应尽可能多添接地铜皮,并与主地相连。射频信号线要尽可能的短;

③ 为了减少时钟信号的干扰,可以将时钟线进行包地处理;

④ ADF4360-0射频输出线阻抗应为50Ω,减少信号反射。

3.4 仿真结果

使用ADIsimPLL对该电路进行仿真。

图5是计算环路滤波器电阻电容参数时系统生成的原理图,从图上我们可以看到满足我们设计的频率要求时环路滤波器的器件参数。

图5环路滤波器参数仿真原理图

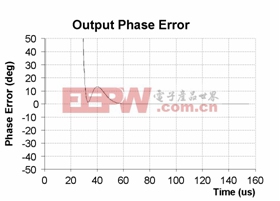

图6 环路滤波器输出相位误差

图6是时域环路滤波器输出相位误差图,从图上我们可以看出大约在60微秒后环路滤波器输出相位误差为0,符合设计要求。

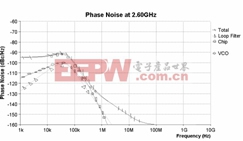

图7 相位噪声频域仿真图

图7是相位噪声的频域仿真图,包括环路滤波器、芯片本身、内部压控振荡器和总的相位噪声与频率在2.6GHz时的关系曲线。从图上我们能够看出频率大于100MHz时所有的相位噪声都在-160dBc/Hz附近。可以满足设计要求。

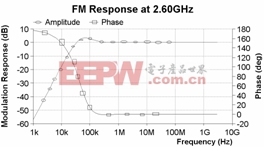

图8 环路滤波器频域响应

图8是环路滤波器在中心频率为2.6GHz时的频域响应图,包括幅度和相位与频率的关系曲线。从图中我们可以看出当频率大于1MHz以后,扫频信号发生器输出是等幅信号,相位不变,我们的工作频率要求是2.4-2.7GHz,从仿真结果来看能够满足设计要求。

图9是芯片时域和频域的仿真环境和结果,从报告中可以看出中心频率设是2.6GHz,扫频范围是2.4-2.7GHz和输出相位噪声数据等信息。

3.5 实测结果

在上述设计的基础上,制作了一个微波扫频信号发生器,实测结果如下:

工作频率:2400MHz~2725MHz,65个频点可以选择。

频率间隔: 5MHz。

输出功率: ≥-11dBm。

相位噪声: ≤-108dBc/Hz (偏离中心频率10kHz处)。

图9 输出报告

3.6 实验结果及分析

本设计中ADF4360-0输出扫频信号的中心频率设置为2.6GHz, ADF4360-0的R计数器设为2,R计数器为参考信号输入提供分频比R,分频后得到5MHz的鉴相频率,N计数器为VCO输出提供分频比,由式(1)可设置相应的寄存器的参数,根据系统输出要求,设定N=520,即B=16,P=32,A=8。由于用通常方法很难产生射频信号源,本文用频率合成器ADF4360-0设计扫频信号发生器,仿真结果表明本设计达到了预期的设计要求。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 如何设计并调试锁相环(PLL)电路(03-25)

- 基于ADF4106的锁相环频率器研究与设计(09-17)

- 使用ADF4007的6.7GHz本地振荡器电路(08-22)

- 利用低噪声LDO 调节器 ADP150 为ADF4350 PLL 和VCO 供电,以降低相位噪声(05-10)

- ADF4157在数字预失真时钟方案中的应用(02-23)