基于ADF4360-0的微波扫频信号发生器设计

1、引言

扫频信号发生器能产生频率随时间作均匀变化、等幅的正弦信号作为被测网络的测试信号[1]。当等幅扫频信号加于被测网络或系统时,网络或系统的输出幅度将按自身的幅频特性变化。从而,能够测出被测网络或系统的幅频特性。

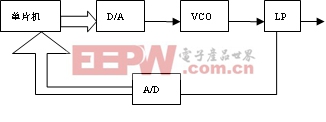

传统的扫频信号源用分立元件实现。例如:在LC振荡器中采用压控变容二极管、在RC振荡器中采用压控电阻实现对振荡频率的控制。这类电路都存在控制精度低、频率稳定性差的缺点。随着集成压控振荡器(VCO)的出现,窄带扫频信号源通常采用图1所示方案[2]。

VCO是电路中的核心器件,输出方波信号,用低通滤波器(LP)提取其基波作为所需正弦波扫频信号。VCO的输出频率由外部定时元件R、C控制,并由D/A转换器输出的直流电压进行小范围调整,单片机通过数字量控制D/A转换器输出的模拟电压,实现对输出频率的控制。该电路的输出频率受VCO定时元件的精度、热稳定性以及电源电压稳定性影响较大,即使可以通过反馈通道进行调整,也无法很好地保证输出频率的精度。除了精度达不到要求外,上面电路频率只能达到K数量级,很难满足微波的要求。为了产生3GHz微波信号,本设计采用了ADI公司的ADF4360-0芯片,并用ADI公司的ADSPBF533平台对其实施控制,最终用在某微波传感器中。

图1 用压控振荡器VCO实现的窄带扫频信号发生器框图

2、ADF4360-0芯片性能分析[3]

ADF4360-0是一款高集成度N个合成器集成VCO芯片,主要由数字鉴相器、电荷泵、R分频器、A, B计数器及双模前置P/P+1分频器等组成。数字鉴相器对R计数器与N计数器的输出信号进行相位比较,得到一个误差电压。14bit可编程参考R分频器对外部晶振分频后得到参考频率。该器件可以通过可编程6位A计数器、13位B计数器及双模前置分频器(P/P+1)来共同完成主分频比N(N=BP+A)。因此,设计时只需外加环路滤波器,并选择合适的参考值,即可获得稳定的频率输出,其输出频率为:

fo=fvco=N(fi/R) ……… …式(1)

式中,fi为参考频率,它可由高稳定度晶体振荡器提供。而其鉴相频率fr为:

fr=fi/R … ………式(2)

ADF4360-0是美国ADI公司生产的高性能锁相频率合成芯片,芯片内VCO可由数字信号控制,这与传统VCO用模拟信号控制不同,该器件的主要特点如下:

(1)该合成器的输出频率范围为2400-2725MHz;并可选择二分频。选择二分频时, 可输出1200-1365MHz的频率信号;

(2)工作电压为3-3.6V;

(3)合成器的输出信号的功率可控制范围为-13dBm ~ - 6dBm;

(4)可编程双模前置分频器的分频比为16/17、32/33等;

(5)能够进行模拟和数字锁定检测;

(6)芯片内部集成VCO。

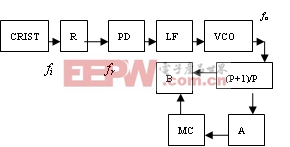

ADF4360-0是一款双模前置分频型单环频率合成器,该器件可在不改变频率分辨率的同时,有效地提高频率合成器的输出频率。图2所示是一个双模前置型锁相频率合成器的工作原理方框图[4]

图2 双模前置型锁相频率合成器结构原理图

在图2所示的器件结构中,(P+1)/P为高速双模前置分频器,其分频模数为P+1和P,此外,系统中的A为脉冲吞咽可编程计数器;B为主可编程计数器;MC为模控制逻辑电路。双模前置分频器通常只有两个计数工作模式,但工作时只要一个模控制信号就可以实现简单的换模计数工作,而不需要采用类似可编程分频器那样复杂的预置操作,因而其工作频率可以做得像固定分频器那样高。事实上,双模前置分频器可以很好地解决固定前置分频器提高输出频率f0和降低频率分辨率Δf0的矛盾。

3、电路设计

3.1 设计要求

要求该信号发生器工作在2.4-2.7GHz的频率范围,在该频率范围内电路输出等幅信号,中心频率为2.6GHz,电路总的输出相位噪声小于-100dBc/Hz,电路相位输出误差小于15°。

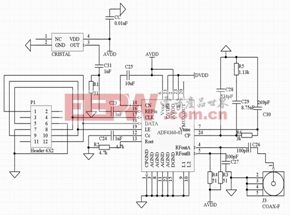

3.2 ADF4360-0应用电路

利用锁相环频率合成器设计的信号发生器能为后续电路提供良好的信号源。图3所示是利用ADF460-0芯片作为信号源的具体电路。

本电路用ADF4360-0来产生2.4G-2.7GHz的线性变化的微波信号。电路中的外部晶振为10MHz的高稳定度有源晶体振荡器。晶体振荡器为ADF4360-0提供参考频率和时钟。由DSP通过SPI串口控制ADF4360-0芯片的锁存器。使用时,晶振应接到ADF4360-0的参考时钟输入引脚CLK_ref,且其内部电荷泵输出引脚CP (ChargePump)与VCO输出引脚VTUNE之间还应接入环路滤波电路。

图3 扫频信号发生器电路原理图

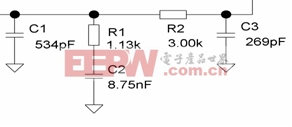

图4 三阶环路滤波电路

图4是一个三阶环路滤波电路,选择fr=10MHz,R=2,所以频率间隔fr/R为5MHz。这里的频率间隔也就是鉴相器的鉴相频率。鉴相频率越高,频率合成器的分频数就越低,则带内相位噪声就越少,但是可选的频点也就越少,设计时要将二者综合考虑。同样,开环带宽的选择需要在杂散(spur)程度与锁定时间(l

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 如何设计并调试锁相环(PLL)电路(03-25)

- 基于ADF4106的锁相环频率器研究与设计(09-17)

- 使用ADF4007的6.7GHz本地振荡器电路(08-22)

- 利用低噪声LDO 调节器 ADP150 为ADF4350 PLL 和VCO 供电,以降低相位噪声(05-10)

- ADF4157在数字预失真时钟方案中的应用(02-23)