小数分频与快锁芯片ADF4193的原理与应用

时间:11-08

来源:电子元器件应用

点击:

0引言

在数字移动通信系统的设计过程中,经常采用跳频方法来提高通信系统的抗干扰、抗多径衰落能力。但这要求快速跳频系统中的超快速跳频PLL能够在几十微秒(μs)内稳定到所要求的相位和频率。为达到这个要求,可采用"乒乓"体系结构。但这种结构需要两个频率合成器。其中当一个频率合成器作为LO工作时.另一个频率合成器的作用是锁定下一步要求的频率。而现在。也可以用一个快锁芯片来实现。美国ADI公司生产的ADF4193快速开关频率合成器就是采用一个PLL的快锁芯片。它能满足"乒乓"结构的切换指标,故可用在无线发射机和接收机的上变频和下变频电路的LO电路中。

1 ADF4193的特点和PLL工作原理

ADF4193是基于小数分频的快锁芯片。该芯片的主要特点如下:

◇具有快速调整的小数-N锁相环结构;

◇可用单片锁相环代替开关式合成器;

◇可在GSM频带内实现5μs跳频,并可在20μs内使相位稳定;

◇2 GHz输出时具有0.5级的相位误差;

◇可编程输出相位;

◇射频输入范围可达3.5 GHz;

◇带有3线串行接口;

◇芯片内置低噪声差动放大器;

◇其相位噪声灵敏度可达-216 dBc/Hz。

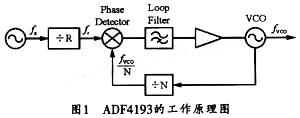

ADF4193主要是基于"乒乓"体系结构的跳频原理。ADF4193的工作原理如图1所示,图中,VCO的作用是提供一个参考频率fx,fx经过预分频R得到鉴相器输入端的参考频率,图1中的环路滤波器的作用是滤除鉴相器输出信号的高频成分和噪声,并将鉴相器的输出电流转化为电压送到VCO的输入端。以控制VCO的输出频率。同时将VCO输出频率经过N分频后反馈给鉴相器。鉴相器的作用是对反馈频率和参考鉴相频率进行比较,当鉴相器两个输入信号的相位同步(且fvco/N=fr)时,VCO的输出频率就是要锁定的频率。

2分频器对PLL的指标影响

2.1相位噪声

一般情况下,分频器的分频比N对PLL的有关指标的影响比较大。这里主要介绍其对相位噪声、锁定时间的影响。 影响相噪的因素通常有分频比、鉴相频率、PLL固有底噪和闭环传递函数等。其近端带内相噪的大小可用下式表示:

式中,PN/Hz表示PLL的固有底噪,N为分频比,fcomp为鉴相比较频率;

从(2)式可以看出,在通带内,相噪主要由鉴相器决定,当鉴相频率fcomp增大一倍时,对应值减小一半,输出频率保持不变,其相噪可改善了3 dB。所以,为了减小通带内的相噪,设计时应该尽量使用分频比比较小的PLL。

2.2锁定时间

锁定时间和闭环带宽有很大关系,环路带宽越大,锁定时间越短,环路带宽越小,锁定时间越长。对于2阶环,其锁定时间T∝1/ωξ(其中ω为环路带宽,ξ为阻尼系数)。所以,一般情况下,可以通过改变环路带宽的值来改变锁定时间。

对于整数分频来说,环路带宽的选取最多只能是参考频fr的1/10。所以,仅靠环路带宽来改变锁定时间的方法有其很大的局限性。

对于小数分频,环路带宽的选取基本上和参考频率fr的关系很小,小数分频的参考频率可以选的很大,如ADF4193的fr可选为13 MHz。如果1/10按来计算,环路带宽可以宽到1.3 MHz,所以小数分频的环路带宽的选取几乎可以不考fr。

虽然环路带宽越宽,锁定时间越短,但是,也不能把环路带宽设置的特别大,因为环路带宽越大,滤波效果越差,这样,PLL输出频率的底噪就越高。

在环路锁定的情况下,参考时钟和再生时钟通常都存在固定的相位差,若将相差假设为△t,则其相位误差计算公式如下:

其中:Vtune是VCO或VCXO的调谐端电压,单位V;Ipump_out为鉴相器的输出鉴相电流,单位mA;Fcomp表示鉴相频率,单位kHz;ZVCO是VCO或VCXO的输入阻抗,单位欧姆。

由式(3)此可以看出,要使参考时钟和再生时钟的相位差尽量小,起主要作用因素的是系统的鉴相频率和振荡器的输入阻抗要足够大。△t的范围与锁定是密切相关的。大多数的PLL芯片都要求在锁定时刻,其连续3个或5个鉴相周期的绝对相位误差要小于15 ns,否则即视为失锁。具体选取3个还是5个鉴相周期,可通过相应的寄存器来设置。在锁定期间,任一周期的相位误差大于25 ns,即为失锁。

一般情况下,环路带宽、锁定时间和相位噪声会相互影响、相互制约。要获得较短的锁定时间,就需要较大的环路带宽,但也会引入更多的噪声,因而有可能导致相位噪声的恶化。同样,如果需要良好的相位噪声,则环路带宽就要变窄,此时的锁定时间就会增加。如果想在不改变环路带宽的情况下改善相位噪声,根据公式(2),可在分频器Ⅳ和鉴相频率Fcomp做一些改善。

在数字移动通信系统的设计过程中,经常采用跳频方法来提高通信系统的抗干扰、抗多径衰落能力。但这要求快速跳频系统中的超快速跳频PLL能够在几十微秒(μs)内稳定到所要求的相位和频率。为达到这个要求,可采用"乒乓"体系结构。但这种结构需要两个频率合成器。其中当一个频率合成器作为LO工作时.另一个频率合成器的作用是锁定下一步要求的频率。而现在。也可以用一个快锁芯片来实现。美国ADI公司生产的ADF4193快速开关频率合成器就是采用一个PLL的快锁芯片。它能满足"乒乓"结构的切换指标,故可用在无线发射机和接收机的上变频和下变频电路的LO电路中。

1 ADF4193的特点和PLL工作原理

ADF4193是基于小数分频的快锁芯片。该芯片的主要特点如下:

◇具有快速调整的小数-N锁相环结构;

◇可用单片锁相环代替开关式合成器;

◇可在GSM频带内实现5μs跳频,并可在20μs内使相位稳定;

◇2 GHz输出时具有0.5级的相位误差;

◇可编程输出相位;

◇射频输入范围可达3.5 GHz;

◇带有3线串行接口;

◇芯片内置低噪声差动放大器;

◇其相位噪声灵敏度可达-216 dBc/Hz。

ADF4193主要是基于"乒乓"体系结构的跳频原理。ADF4193的工作原理如图1所示,图中,VCO的作用是提供一个参考频率fx,fx经过预分频R得到鉴相器输入端的参考频率,图1中的环路滤波器的作用是滤除鉴相器输出信号的高频成分和噪声,并将鉴相器的输出电流转化为电压送到VCO的输入端。以控制VCO的输出频率。同时将VCO输出频率经过N分频后反馈给鉴相器。鉴相器的作用是对反馈频率和参考鉴相频率进行比较,当鉴相器两个输入信号的相位同步(且fvco/N=fr)时,VCO的输出频率就是要锁定的频率。

2分频器对PLL的指标影响

2.1相位噪声

一般情况下,分频器的分频比N对PLL的有关指标的影响比较大。这里主要介绍其对相位噪声、锁定时间的影响。 影响相噪的因素通常有分频比、鉴相频率、PLL固有底噪和闭环传递函数等。其近端带内相噪的大小可用下式表示:

式中,PN/Hz表示PLL的固有底噪,N为分频比,fcomp为鉴相比较频率;

从(2)式可以看出,在通带内,相噪主要由鉴相器决定,当鉴相频率fcomp增大一倍时,对应值减小一半,输出频率保持不变,其相噪可改善了3 dB。所以,为了减小通带内的相噪,设计时应该尽量使用分频比比较小的PLL。

2.2锁定时间

锁定时间和闭环带宽有很大关系,环路带宽越大,锁定时间越短,环路带宽越小,锁定时间越长。对于2阶环,其锁定时间T∝1/ωξ(其中ω为环路带宽,ξ为阻尼系数)。所以,一般情况下,可以通过改变环路带宽的值来改变锁定时间。

对于整数分频来说,环路带宽的选取最多只能是参考频fr的1/10。所以,仅靠环路带宽来改变锁定时间的方法有其很大的局限性。

对于小数分频,环路带宽的选取基本上和参考频率fr的关系很小,小数分频的参考频率可以选的很大,如ADF4193的fr可选为13 MHz。如果1/10按来计算,环路带宽可以宽到1.3 MHz,所以小数分频的环路带宽的选取几乎可以不考fr。

虽然环路带宽越宽,锁定时间越短,但是,也不能把环路带宽设置的特别大,因为环路带宽越大,滤波效果越差,这样,PLL输出频率的底噪就越高。

在环路锁定的情况下,参考时钟和再生时钟通常都存在固定的相位差,若将相差假设为△t,则其相位误差计算公式如下:

其中:Vtune是VCO或VCXO的调谐端电压,单位V;Ipump_out为鉴相器的输出鉴相电流,单位mA;Fcomp表示鉴相频率,单位kHz;ZVCO是VCO或VCXO的输入阻抗,单位欧姆。

由式(3)此可以看出,要使参考时钟和再生时钟的相位差尽量小,起主要作用因素的是系统的鉴相频率和振荡器的输入阻抗要足够大。△t的范围与锁定是密切相关的。大多数的PLL芯片都要求在锁定时刻,其连续3个或5个鉴相周期的绝对相位误差要小于15 ns,否则即视为失锁。具体选取3个还是5个鉴相周期,可通过相应的寄存器来设置。在锁定期间,任一周期的相位误差大于25 ns,即为失锁。

一般情况下,环路带宽、锁定时间和相位噪声会相互影响、相互制约。要获得较短的锁定时间,就需要较大的环路带宽,但也会引入更多的噪声,因而有可能导致相位噪声的恶化。同样,如果需要良好的相位噪声,则环路带宽就要变窄,此时的锁定时间就会增加。如果想在不改变环路带宽的情况下改善相位噪声,根据公式(2),可在分频器Ⅳ和鉴相频率Fcomp做一些改善。

- IR数据中心电源管理方案可提供更高的效率和更低的散热(04-27)

- 使用功率MOSFET封装技术解决计算应用的高功耗问题(05-04)

- 采用新型放大器实现高性能的电流检测(05-10)

- 单芯片DC-DC变换器在CPU电源控制系统中的应用(06-07)

- LED晶粒/芯片制造流程(06-13)

- 微处理器电源监控芯片SGM803及其应用(06-18)