3 FPGA对ADF4193的配置过程

通过Verilog语言进行编程,可用FPGA来实现对ADF4193的配置。ADF4193中有八个寄存器,通过对这八个寄存器的配置,可以使ADF4193进入正常工作状态。ADF4193有一个3线串行接口,这三个接口分别为LE、CLK、DATA。数据可在时钟的上升延从ADF4193的3线串行接口输入到24-bit的输入移位寄存器,高字节在前。在使能信号LE的上升延,移位寄存器的数据将被锁入到8个寄存器R0~R7的其中之一。具体写给哪个寄存器,可由移位寄存器的24-bit最低位的三个控制比特c3、c2、c1来决定。

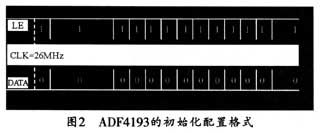

按照一定的方式将初始化配置数据发送到ADF4193对应的寄存器,即可实现ADF4193的初始化。图2所示是用逻辑分析仪抓到的配置图。

图2给出了ADF4193的17步配置过程。其中寄存器R0和R2的值决定了锁相环的输出频率。图2中,在配置完前两个寄存器后,还需要等待10ms的时间,以便环路滤波器的电容能够放电。通过这样的配置可以将ADF4193配置在任何一个需要的频率上。需要说明的是,只有当初始化过程稳定,才可以进行跳频操作。否则,ADF4193将无法进行正常的跳频功能。

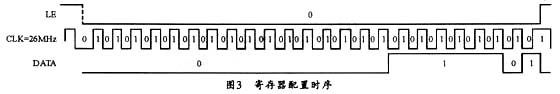

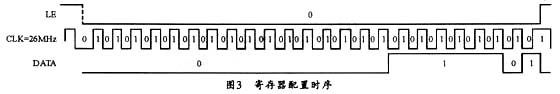

对应图2,即可得到第一个被配置的寄存器的配置时序,其具体的时序图如图3所示。

从图3可见,给一个寄存器配置数据可通过LE信号进行控制。在LE为低电平时。恰好有24个时钟周期卡在LE的前一个下降延和后一个上升延之内。从数据的后三位可以看出,这次配的寄存器是R5。其它寄存器的配置过程为此相同。

4 PLL指标的测量

4.1相噪的测量

利用仪表的相噪模板可对ADF4193的输出相噪进行测量。其测量结果如图4所示。

从图4可以看到,Freq Offset在:100 Hz、1kHz、10 kHz、100 kHz和1 MHz处都可以达到很好的指标。

4.2锁定时间的测量

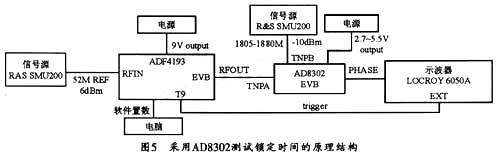

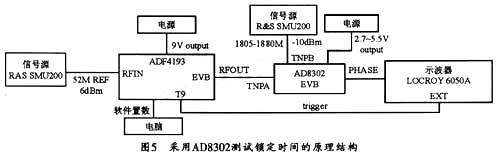

为了节约成本,可以采用ADI公司提供的AD8302并结合示波器对锁定时间进行测量,基于AD8302的测量原理结构如图5所示。

实际使用证明,ADF4193的锁定时间可以达到所需要的指标。此外,采用FPGA来实现对ADF4193的配置,其过程相对比较简单且易实现,而同时性能也能得到保证。

5结束语

由ADF4193的配置时序可以看出,ADF4193是一款易配置和使用的芯片,使用它可以简化设计复杂度,缩短项目调试周期。从测量的相位噪声和锁定时间的结果可以看出:ADF4193具有很好的性能指标,而且稳定性比较好。ADF4193的最主要的优点是可以简单的实现跳频,它不再需要使用"乒乓切换"电路,因而可缩短系统的切换时间,以在时隙的保护时间内实现频率切换。事实证明,ADF4193比"乒乓切换"电路更能简化电路,减少成本,同时可节省PCB的布板面积。很适合在通信系统中使用。