基于NCOIPcore的Chirp函数实现设计

时间:02-21

来源:互联网

点击:

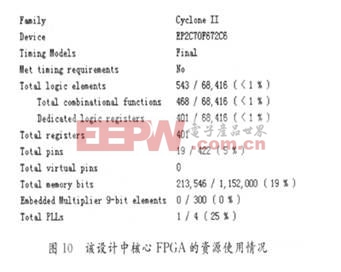

数器的时钟输入端;第二级计数器的作用是,产生地址信号以驱动频率控制字存储器输出相应的控制字,当前级进位信号有效时该计数器输出加“1”。以达到改变频率输出的目的,其连接电路图如图9所示。 4 仿真与验证 将该设计通过将程序下载到Altera公司生产的DSP开发板(型号DK-DSP-2C70N)中进行仿真,其核心FPGA(型号为EP2C70F672C6)的资源使用情况如图10所示。 并通过该开发板上D/A转换器输出模拟波形(只截取了4个时刻的图样)如图11所示。 通过图11可以看出该设计能很好地完成扫频输出的功能,并且杂波分量很小,干扰很小。 5 结 语 该设计通过采用技术成熟的NCO IP Core完成,其优势在于: (1)利用了成熟的FPGA知识产权技术,使得设计更加简便并易于移植;

(2)利用NCO IP core的高稳定性,使得Chirp函数的各项噪声较之于其他设计更小,有利于对射电天文这样微弱信号的处理,减少了处理带来的各种噪声。

- 基于锁相环的Chirp超宽带信号源的设计与实现(07-26)

- 关于指针函数的范例 作者(xiaoqi)(zz)(03-10)

- 由DAC谐波频谱成分重构其传递函数(04-16)

- 基于Matlab的FIR数字滤波器设计(10-07)

- 基于锁相环的低频函数发生器(09-17)

- FIR数字滤波器的设计与实现 (12-18)