ADF4157在数字预失真时钟方案中的应用

另外, 需要注意的是对PLL芯片的寄存器进行写操作时, 需要按照一定的次序来写, 具体请参照芯片资料中的描述。

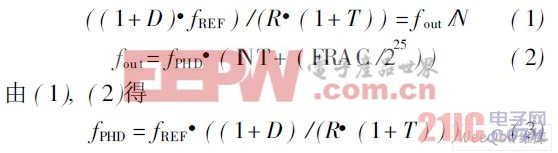

ADF4157通过INT 与FRAC 寄存器配置N 分频器, N = INT + ( FRAC /225 ), 图2中的环路滤波器( LPF)的作用是滤除鉴相器输出信号的高频成分和噪声, 并将鉴相器的输出电流转化为电压送到VCO的输入端, 以控制VCO 的输出频率。同时将VCO输出频率经过N 分频后反馈给鉴相器。鉴相器的作用是对反馈频率和参考鉴相频率进行比较, 当鉴相器两个输入信号的相位同步时, VCO 的输出频率就是要锁定的频率。PLL 的R, INT, FRAC 寄存器通过合理配置使外部VCO 工作在2 482. 44MHz输出, 将其快速锁定锁相模块。其关系式为:

由于N 分频的 ∑ - △调制器速度的限制f PHD最大为32MH z。FRAC取0到225 - 1, D、T 取0或1,R取1到32, INT可取23到4095, 通过ADI公司设计的ADF4157 Evaluation Softw are ADF _ FRAC _REC3[软件进行R, INT 和各个分频器合理的设置。由于fREF为181. 44MH z由AD9516时钟分配器输出, R选32, fPHD = 2. 835MH z, D 取0, T取1。

将上述数据都转化为十六进制数可得到其配置数据。最终将外部VCO 输出的时钟信号, 通过环路滤波器输入到数字预失真系统的上下变频模块作为本振时钟。

2. 3 测试结果

2. 3. 1 ADF4157相位噪声仿真

相位噪声是影响频率合成器性能的重要指标, 主要来自锁相环各组成部分的相位噪声, 分别为VCO相位噪声, 参考输入频率相位噪声, PLL芯片相位噪声, 环路滤波器相位噪声。根据数字预失真系统上下变频本振频率要求, VCO 输出频率2 482. 44MH z, 参考输入频率为181. 44MHZ, 鉴相频率2. 835MHz, 由于VCO控制电压( 14 V)超出了Vp电压( 5 V) , 所以锁相环环路滤波器采用有源滤波器, 放大器为OP184, 环路带宽选择为84 kH z,VCO 选择SCD160 ( UMX??160??D16 ) 通过AD IsimPLL软件仿真如图4。

图4 相位噪声。

可以看出, 在低的偏离频率处, 参考源的噪声是频率合成器输出噪声的主要来源, 在高的偏离频率处, VCO相位噪声成为影响频率合成器总的相位噪声主要因素, 在10 kH z时总的相位噪声为- 89. 256 0dBc /H z, 性能较好。

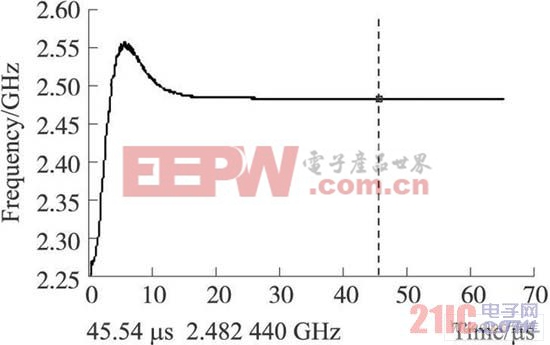

2. 3. 2 ADF4157锁定时间仿真

影响锁相环频率合成器锁定时间最主要的因素是环路带宽和相位裕量。环路带宽越宽锁定时间越快, 但其滤波效果差。ADF4157在参考输入频率为181. 44MH z, 锁相环VCO 输出2 482. 44MHz, 鉴相频率为2. 835MH z, 环路带宽选择为84 kHz, 相位裕量47!,在45. 54 s的时候, 锁相环基本上达到锁定, 通过AD IsimPLL软件仿真如图5。

图5 84 kH z时锁定时间。

在图6中环路带宽为200 kH z其他条件不变,24. 05 s的时候, 锁相环基本达到锁定。进一步证明环路带宽越宽锁定时间越快, 但其滤波效果更差。

图6 200 kH z时锁定时间。

2. 3. 3 ADF4157输出频谱图

采用此本振频率时钟方案, 系统整体性能也较为理想, PLL频率合成器ADF4157产生的本振频率经过频谱分析仪测试频率合成器输出信号, 输出信号频率为2 482. 44 MH z, 信号功率为- 2. 5 dBm左右, 在40MH z的窄带范围内没有明显的杂散存在,满足预失真系统上下变频本振信号频率要求, 经过调试匹配等优化措施输出频谱图如图7。

图7 ADF4157输出频谱图

2. 3. 4 时钟板实物图:

我们采用C adenceA llegro PCB Ed itor15. 5绘制出整个时钟方案的PCB 图, 时钟板为4层板, 顶层和底层是信号层, 中间两层是地层和电源层, 鉴于时钟线的布线要求, 时钟线应尽量短而粗, 采用差分走线, 保证信号完整性。经过合理布局, 绘制的PCB电路图如图8。

图8 时钟方案实际PCB图。

3 结束语

锁相式频率合成器是现代在应用最广泛的一种频率合成器, 而分数数字锁相频率合成技术作为一种很有前途的锁相频率合成技术, 备受大家的关注, 本文介绍了基于FNPLL的ADF4157数字预失真系统本振频率以及相应的时钟方案设计, 确保预失真系统信号质量。ADF4157具有低的相位噪声, 更高的频率分辨率, 快速锁定, 在参考输入频率不变情况下, 比一般单环NPLL具有更小的步进变化等特点, 对今后的设计类似功能的频率合成器具有很高的参考价值。

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 如何设计并调试锁相环(PLL)电路(03-25)

- 基于ADF4106的锁相环频率器研究与设计(09-17)

- 使用ADF4007的6.7GHz本地振荡器电路(08-22)

- 利用低噪声LDO 调节器 ADP150 为ADF4350 PLL 和VCO 供电,以降低相位噪声(05-10)

- 基于ADF4111的数字锁相式可调频率源实现(06-09)