IC时钟分配系统中的锁相环

量相对载波 (fc)的数量。图4所示为相位噪声图(请注意,仅显示单边带)以及用于确定RMS相位抖动的积分范围(f1至f2)。偏移频率范围取决于应用要求。

计算等效RMS抖动时,第一步应该是获得目标频率范围内(即曲线下的区域)的相位噪声功率积分值。曲线被分割成许多个单独的区域,每个区域利用两个数据点即可确定。一般而言,求积分时,所采用的频率上限应该是理想应用采样频率的两倍,以ADC为例(假设振荡器与ADC输入之间并无抖动)。这数字接近于ADC采样时钟输入的带宽。

选择求积分所用频率下限时,同样需要进行判断。理论上,应该尽量低,以获得真实的RMS抖动。但是在实践中,振荡器规范一般不适用于10Hz以下的偏移频率,尽管这也可以产生足够准确的结果。大多数情况下,求积分频率低于100Hz是比较合理的,但前提是振荡器规范能够满足此要求。否则,就使用1-kHz或10-kHz的数据点。

系统设计时,如果需要采用低抖动的采样时钟,则一般禁止使用低噪声专用晶体振荡器。替代方法是采用PLL与电压控制型振荡器,以“清理”系统时钟噪声。

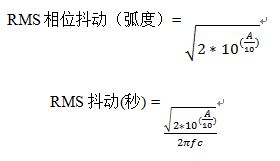

窄带宽环路滤波器配合电压控制型晶体振荡器(VCXO)的相位噪声一般是最低的。PLL趋向于降低“近载波”相位噪声,同时可以降低总体相位噪声底限。PLL输出配以适当的带通滤波器可以进一步降低白色噪声底限。以预期偏移频率范围(f1 至 f2)上的相位噪声积分区为例,运用下列公式计算RMS相位抖动:

附加相位抖动:

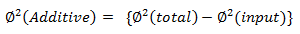

现在,我们假设采用时钟缓冲器而并非时钟发生器来分配单源时钟输入所产生的多个时钟副本。对于高性能时钟器件而言,它们并非采用输出相位抖动数量测量性能——因为此数值取决于时钟源的输入相位抖动——而是采用附加相位抖动评估时钟源的质量。附加相位抖动考虑到了整个输出相位抖动中,缓冲器件所贡献的相位抖动数量。如此一来,对比缓冲器件时,无需考虑测量时所采用的输入质量。

时钟相位抖动是许多系统设计的关键参数,因此,我们需要准确测量各个组件的相位抖动贡献,这一点非常重要。根据可用的硬件和测试设置,计算时钟树组件附加抖动一种最简单方法就是“平方和”法。测量被测器件(DUT)输出端总的RMS相位抖动,然后测量DUT源输入信号的RMS相位抖动,即可运用下列公式计算出DUT的附加RMS抖动:

式中,Φ表示RMS相位抖动。采用上述方法时,最好设置质量极高的低相位噪声基准,以便是由DUT而非源输入贡献绝大部分的抖动。要想获得所需的性能水平,应采用OCXO作为基准源。

- IC时钟分配系统中的PLL(04-29)

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)