基于立体封装技术的复合电子系统模块应用

摘要:本文在SIP立体封装技术的基础上,设计了基于DSP、FPGA的复合电子系统模块。重点介绍了模块的功能构成及模块接口应用,为基于SIP小型化封装的复合电子系统(功能可订制)提供应用基础。

引言

随着电子技术的发展对系统模块小型化高可靠性提出了更高的要求。复合电子系统模块是欧比特公司推出的一款SIP模块,其将特定(可定制)的电子系统功能模块采用立体封装技术制作而成。本文介绍了基于DSP、FPGA的复合电子系统模块OBT-MCES-01的功能构成以及应用方法。

1 SIP简介

SIP(System In Package系统级封装)是将多种功能芯片,包括处理器、存储器等功能芯片集成在一个封装内,从而实现一个基本完整的功能。欧比特公司SIP采用立体封装技术,将系统功能模块分割为多部分(层)进行叠装设计,层间互联信号通过表面金属化后激光雕刻实现,形成QFP、PGA等封装形式的模块。

2 模块功能设计

OBT-MCES-01是一款基于DSP、FPGA的集成ADC、DAC、CAN、RS422等功能的SIP复合电子系统模块。其采用QFP240 PIN封装形式,实体大小35*35*10mm,各子功能模块在模块内实现连接,CAN、RS422、ADC、DAC、JTAG、I/O等输入输出端口作为模块引脚。

3 模块功能应用

OBT-MCES-01一款基于DSP、FPGA的完整电子系统,可适用于用到高速DA、AD等相关领域,同时兼备了RS422、CAN功能。模块所含资源如下:

● 32位浮点DSP

● 100万门FPGA

● 4MB FLASH

● 1MB SRAM

● 16位高速DAC

● 12位高速ADC

● 14位高速ADC

● RS422收、发

● CAN

● 触发器输出

3.1 DSP

DSP采用高速32位浮点型FT-C6713,为整个系统的控制中心,负责程序控制和FPGA之间通讯。DSP和FPGA、FLASH、SRAM互联,其中DSP存储部分连接了一片2M*16Bit FLASH 及256K*32Bit SRAM ,用于系统程序ROM及数据高速缓存。FLASH、SRAM的控制信号由FPGA产生。DSP配置为16Bit ROM启动模式。

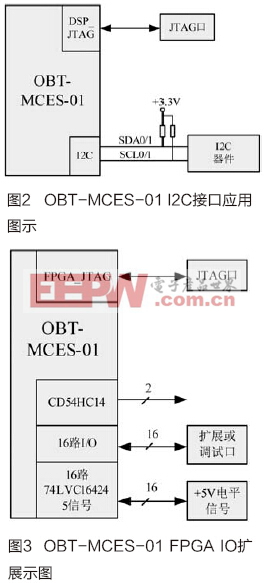

DSP的I2C、JTAG对外引出做引脚。其中JTAG信号用于对系统的仿真调试以及程序烧录。两路I2C都有引出,可扩展外围I2C器件。其应用连接方式如下:

3.2 FPGA

FPGA采用100万门的SMQ2V1000为整个系统模块的处理中心,包括配置模块、ADC、DAC、CAN、RS422等功能。FPGA负责系统外围接口信号处理及和DSP完成数据通讯。FPGA引出至引脚的信号有JTAG信号、16I/O信号、16路74LVC164245信号、2路CD54HC14触发门输出。其中JTAG端口用于FPGA的调试以及程序下载,FPGA配置芯片为18V04。16路I/O用于后续功能的扩展以及调试。16路74LVC164245D端口为+5V 电平信号,可将外部+5V电平信号转换成+3.3V信号给FPGA处理。2路CD54HC14输出直接至引脚输出。

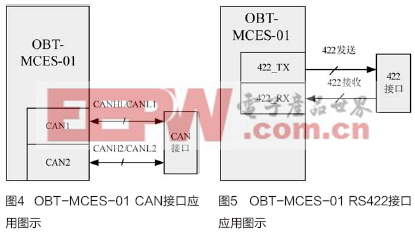

3.3 CAN

OBT-MCES-01包括2路CAN(使用SN65HVD232D接口芯片+3.3V供电),分别引出引脚可接外部CAN信号输入,注意模块CAN信号之间并没有并接匹配电阻,如需要需在CANH、CANL之间跨接120欧电阻。FPGA内需嵌入CAN IP核完成CAN信号处理,DSP可对此IP核进行CAN功能操作。

3.4 RS422

OBT-MCES-01集成了RS422发送、接收接口电路,分别采用SM3030、SM3096。接口芯片采用+3.3V供电,信号直接和FPGA相连,FPGA内需嵌入RS422 IP核,DSP可进行此IP核进行RS422功能操作。

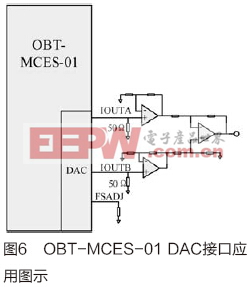

3.5 DAC

OBT-MCES-01 DAC部分采用的是16位高速差分芯片B9726,采用+3.3V/+2.5V供电,使用内部参考电压VREF=1.2V。DSP和FPGA之间通讯完成DAC操作。DAC转换输出IOUTA、IOUTB至引脚,可外接运放滤波器电路。B9726的FSADJ信号做引脚输出,可外接电阻调节DAC输出幅度。

DAC 输出关系:IOUTFS = VREF/RFSADJ ×32

IOUTA = I OUTFS × DB[15:0]/65536

IOUTB = I OUTFS × (1 - DB[15:0])/65536

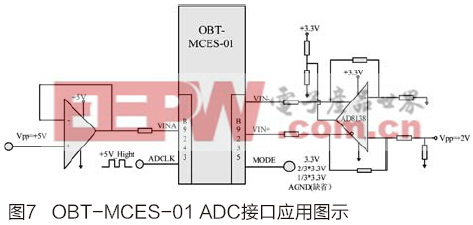

3.6 ADC

OBT-MCES-01包括两ADC,一路为12位高速B9235,一路为14位B9243。ADC数据及控制信号连接至FPGA,DSP和FPGA之间通讯完成ADC操作。

其中B9235采用单+3.3V供电,两差分输入端做引脚输入,操作模式MODE做引脚输入。典型的应用为使用差分驱动将单端模拟输入转换成差分。需要注意的是模拟输入范围Vpp=2V。

B9243采用单+5V供电,连接成单端输入模式VINA(Vpp=5V)做引脚输入,ADC时钟做引脚输入,外部输入+5V电平的时钟信号。

4 总结

本文阐述了欧比特公司设计的基于DSP、FPGA的复合电子系统模块OBT-MCES-01的功能构成及接口应用,此方案对今后订制类复合电子系统模块的研制及应用提供借鉴意义。

参考文献

[1] OBT-MCES-01使用手册V1.0,欧比特控制工程股份有限公司,2013

[2] 邹彦,DSP原理及应用,电子工业出版社,2005

[3] 刘岚,黄秋元,陈适,FPGA应用技术基础教程,电子工业出版社,2009

[4] Walt Kester, DAC Interface Fundamentals, Analog Devices, Inc.,2009

[5] John Ardizzoni, Jonathan Pearson, “Rules of the Road” for High-Speed Differential ADC Drivers, Analog Devices, Inc.,2009

复合电子系统 DSP FPGA ADC DAC RS422 CAN 201409 相关文章:

- 单片式降压型稳压器为DSP提供片内电源排序(01-09)

- 什么是PCI总线?其接口芯片的应用(01-26)

- 功率分配系统(PDS)设计:利用旁路电容/去耦电容(04-29)

- 具有多个电压轨的FPGA和DSP电源设计实例(05-22)

- 具有多个电压轨的FPGA和DSP电源设计实例(二) (05-22)

- 基于DSP和CPLD的移相全桥软开关电源数字控制器(06-02)