IC时钟分配系统中的锁相环

我们在本系列文章的前一部分[链接]已经讨论了锁相环(PLL)的应用以及在时钟分配系统中,PLL相对于传统振荡器的优势。接下来我们将会阐述基于PLL的时钟分配系统的重要参数,这些参数都是设计时必须考虑的。例如,在实践过程中,时钟的准确时序对所有分配系统而言都非常重要。如果时钟位置偏差范围大,则可能会导致系统发生故障。时域中的这些偏差被称为“抖动”。此外,抖动又分多个类别,譬如周期性抖动、周期间抖动、RMS抖动、长期抖动以及相位抖动。在本章节,我们将重点阐述“相位抖动”,其在频域中可被称之为“相位噪声”。

相位噪声与相位抖动

相位噪声与相位抖动是时钟分配系统的关键参数,因为时钟信号的质量在很大程度上取决于其相位噪声与相位抖动。数字I/O的最大速度受到时钟时序误差的限制。随着技术不断进步,对时序精确性的要求也越来越高,时钟必须具有准确的边缘和高稳定性。

理想情况下,时钟边缘与其预期位置之间不得存在偏差。但是在实践过程中,时钟源极易受到噪声的影响,进而导致时钟边缘偏离于理想位置。这就称之为抖动。基于PLL的频率合成器主要用于确保输出频率在规定工况下的准确度。其中一条关键要求就包括良好的相位噪声和相位抖动性能,在频域中,相位噪声就代表时钟信号噪声,而相位抖动是时域的说法,表示时钟信号不稳定。时间与相位可互换使用,从而对抖动与相位噪声进行量化。

系统中过多的抖动会提高误码率,有可能超过系统级要求。射频和A/D数据转换应用需要采用相位噪声非常低的时钟。对于射频应用,相位噪声增加后,可能会产生通道间干扰,进而削弱射频信号质量。对于ADC应用,如果相位噪声较高,可能会限制信噪比(SNR),增加量化误差。

相位噪声现象是PLL设计人员目前所面临的一个主要问题。所有现实环境中的振荡器和信号发生器均存在相位噪声,但相位噪声是不受欢迎的,因为它可能会导致传统接收器中收到的信息失真或完全丢失。因此,必须了解和量化相位噪声,从而最大限度地降低相位噪声对较高层次产品的影响。

相位噪声:

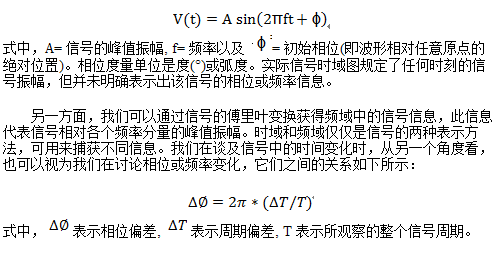

了解相位噪声之前,我们首先来了解一下理想的正弦信号。正弦波是周期性模拟信号的基本形式。正弦信号可以表示为:

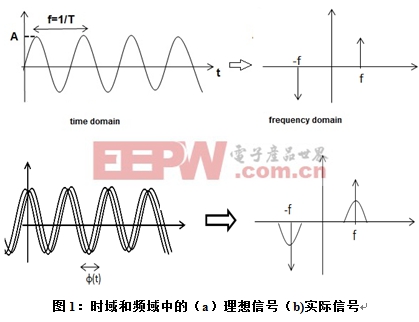

如图1(a)所示,理想的正弦信号是单调波。这意味着,理想的正弦信号只有一个频率分量,其整个功率均在该分量之中。这一点可以通过傅里叶变换观察到。然而,环境及/或信号源噪声会导致信号的振幅和相位出现一定波动。

通过傅里叶展开,我们可以看到任何信号均可以分解成多个具有不同频率和振幅的正弦信号。因此,傅里叶变换将显示功率谱在多个频率上分布。图1(b)从时间和频率两个角度分别显示了正弦信号。如果信号功率分布在一个频带上,这意味着该信号携带多个不需要的频率分量。

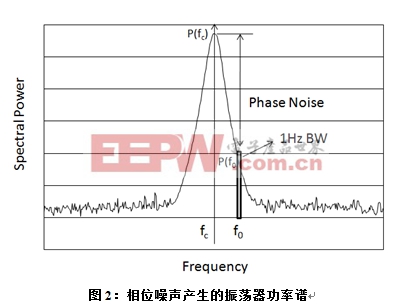

振荡器的相位噪声具有短期不稳定性,从频域角度来描述是最好的,这样可以通过测量中心频率任一侧的噪声边带来显示频谱密度。在实践中,大多数相位噪声测量都会出现一条边带。如上所述,理想信号会精确按照载波频率表现出单个脉冲,信号功率全部包含在该脉冲之中。对于实际信号,噪声会导致功率在范围较宽的频带上分布。

相位噪声的单位一般采用dBc/Hz,1Hz带宽载波在给定偏移频率下产生的噪声功率与载波功率之比即为相位噪声。dBc是载波分贝的缩写,用于确定边带相位噪声特性。

图2显示了非理想振荡器的典型输出频谱。此频谱显示了1-Hz带宽在偏移频率为f0下的噪声功率以及fc下的载波功率。

虽然图2引入了双边带这一概念,但在实践中,大部分相位噪声的测量都是利用单边带完成的。表达公式如下所示:

£(f)=10log{P(f0)/P(fc)}

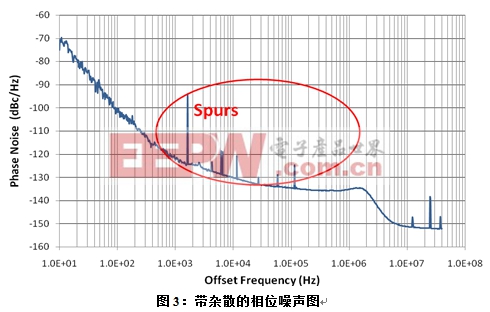

这些相位变化既可能是离散型(确定性)的,也可能是连续型(随机性)的。离散型变化被称之为杂散频率,如图3所示,可在频谱密度图中看到这些变化。大部分杂散都与信号源中的已知现象有关,譬如电源频率、振动频率等等。由于我们对这些过程均已了解,因此将它们称之为确定性变化,在系统设计时适当注意即可避免。另一方面,连续型相位波动是由于随机的噪声现象造成的,譬如白噪声和闪烁噪声等环境噪声。

RMS相位抖动:

相位噪声与相位抖动之间关系密切。相位噪声是频域中表示时钟噪声的方法。另一方面,相位抖动则是时域中表示时钟信号不稳定的方法。从相位噪声图中,选择目标偏移频率范围,然后求取该范围内的相位噪声积分,即可获得RMS相位抖动。

对于方波,大部分能量均在载波频率上。但是,一定频率范围内会泄漏部分信号能量。相位抖动就是两种偏移频率之间所包含的相位噪声能

- IC时钟分配系统中的PLL(04-29)

- 小数分频与快锁芯片ADF4193的原理与应用(11-08)

- 全数字锁相环的设计及分析(03-01)

- 基于锁相环的频率合成电路设计(07-30)

- 锁相环中YTO自校准技术的应用(10-02)

- 基于DDS+PLL技术的频率合成器的设计(07-23)