C波段宽带捷变频率综合器设计

摘要:本文介绍了一种C波段宽带捷变频率综合器的设计方法,采用直接数字频率合成器(DDS)实现频率捷变,采用倍频链路扩展输出带宽,通过与锁相环(PLL)合成产生的本振信号混频将输出频率搬移到C波段。论述了DDS时钟电路、倍频链路以及混频部分的设计方法,并给出了达到的主要技术指标和测试结果。

引言

频率合成器是现代通讯系统必不可少的关键电路, 是电子系统的主要信号源,是决定电子系统性能的关键设备。随着系统对频率源的频率稳定度、频谱纯度、频率范围和输出频率个数的要求越来越高,高稳定、低相位噪声、低杂散,小步进和高速变频是频率合成器发展的主要趋势。

当前主流的频率合成方法分为锁相环频率合成(PLL)和直接数字合成(DDS)两种。其中锁相环电路输出频率高,相位噪声好,其缺点是频率分辨率低,频率跳变时间较长。而DDS有极好的频率分辨率,高速的频率切换时间,很好的相位噪声,但它输出频率较低,杂散信号较多。

1 频率合成方案的分析

本课题的研究背景来源于某接收机项目,为收发模块提供C波段中一定范围内小步进快速连续可变的跳频源信号。

由于DDS芯片具有频率步进小,切换迅速的特点,成为捷变频率综合器的必然选择。但是目前DDS芯片的直接输出频率无法到达C波段,需通过一定的频率合成方案实现,目前基于DDS技术的频率合成方案主要有以下3种。

1.1 DDS直接激励PLL方案

DDS的输出作为锁相环电路的基准频率,PLL电路锁相倍频得到输出频率。利用DDS的高分辨率实现小的频率步进来改变参考频率,同时PLL的带通特性也能抑制部分DDS的输出杂散。

这种方法具有高频率分辨率和低杂散的优点。不过不足的是频率的切换时间由锁相环的环路滤波器的带宽决定,频率切换速度不够快。

1.2 DDS+PLL环外混频合成方案

直接数字合成产生的信号,通过与锁相环PLL环外混频将DDS输出的频谱搬移到较高的频段。

这种方法保留了DDS频率分辨率高和频率切换速度快的优点,同时将输出频率扩展到更高频段,PLL只产生固定频点,相位噪声低。其缺点是:1、DDS产生的近端杂散会通过混频过程而搬移到输出频段内,较难滤除。混频器的引入也可能产生其他非线性杂散。2、DDS的直接输出频谱只是相当于发生了搬移,输出频率的带宽仍然等于DDS的直接输出带宽,DDS直接输出带宽相对较窄,该方法不能扩展频段,当所需输出带宽超过DDS输出带宽范围时无法利用该方法实现。

1.3 DDS+倍频频率合成方案

直接将DDS的输出频率倍频到更高的频点,利用倍频链路来将DDS的输出频率倍频到所需输出频率,同时也能扩展DDS的输出带宽。

该方案能输出较多频点,获得较高的频率转换时间以及较宽的输出频带。但这种方法也存在其缺点:DDS直接倍频的过程可能会将DDS自身的杂散信号放大,同时倍频器也会产生各次谐波,需要在倍频链路中设计滤波器组来有效抑制输出杂散,该方案电路较复杂,调试起来较麻烦。

2 系统要求以及C波段捷变频率合成器的实现

系统要求频率合成器能够快速切换频率,频率步进小,杂散指标良好,要求分别产生4路输出频率信号6.5125~6.7375GHz、6.5875~6.8125GHz、6.6625~6.8875GHz、6.7375~6.9625GHz,杂散抑制优于-50dBc。

根据频率合成器指标,输出带宽大于200MHz,虽然DDS直接输出带宽大于200MHz,但考虑到DDS在宽频带输出时杂散特性不好,选择DDS输出中杂散指标较好的一段使用,再通过倍频来扩展输出带宽。

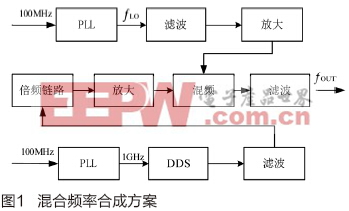

系统所需求的输出频率要求达到6.5GHz以上,如果直接通过DDS倍频达到所需频率,则需要倍频的倍数相对较高,对应倍频链路的设计较为复杂,难以保证输出信号的频谱纯度。综合考虑,选择采用DDS+倍频技术+上变频技术以便得到所需要的宽带捷变频率信号。DDS倍频输出后再与锁相环产生的较高频点的本振进行混频得到最终的输出频率信号,系统框图如图1所示。

2.1 DDS信号输出

本文采用ADI公司的高性能DDS芯片AD9858。DDS芯片AD9858具有频率转换时间短,输出频带宽的优点,能够满足对低相位噪声、低杂散噪声、快速频率切换以及宽带线性扫描的要求。参考AD9858产品手册并结合系统要求输出频段考虑,本设计中采用AD9858输出128.125MHz~183.375MHz频段,该段频谱杂散指标较小,经过4倍频后能达到系统输出的带宽。

DDS输出信号的质量取决于参考时钟信号的性能。从追求频率合成器的性能角度,应选用高性能的晶振通过倍频产生DDS时钟。但考虑到晶振倍频电路较复杂且本系统对频率合成器的相位噪声指标没有过高的要求,AD9858的时钟信号通过锁相环电路锁定输出1GHz产生,如图2所示。锁相环

变频率综合器 DDS PLL C波段 合成器 201410 相关文章:

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于FPGA及DDS技术的USM测试电源的设计 (09-08)

- 高性能双通道DDS芯片AD9958及其应用(02-04)

- 直接数字频率合成器DDS的优化设计(01-25)

- 如何预测直接数字频率合成器(DDS)输出频谱中主相位截断杂散的频率和幅度(06-18)

- 基于DDS的调频信号发生器的设计与仿真(04-12)