基于DDS的调频信号发生器的设计与仿真

引言

DDS(直接数字频率合成器)具有相位变换连续、频率转换速度快、频率分辨率高、相位噪声低、频率稳定度高、集成度高、易于控制等诸多优点,在现代频率合成技术中占有重要地位,被广泛应用于信号发生器、雷达系统、通信系统等领域。MCU(微控制器)具有很强的数据处理能力和控制能力,片上外围设备丰富,精度高,功耗低,在电子设备上有广泛的应用。本文介绍一种基于ADI公司的双通道DDS芯片AD9958产生高质量调频信号的数字调频信号发生器的设计方法,该结构产生的调频信号覆盖频率范围广,载波频率和频偏数字可调,调频波形频率准确度高,且成本较低、可靠性高。

系统结构原理

调频(FM)体制用已调信号频率的变化承载信息。调频波的瞬时频率等于载波频率加上一个正比于调制信号的时变频率。

调频波的表达式为:

其瞬时角频率为:

其中ω0 固定角频率(载频); 为比例常数(调制常数),代表调制器的灵敏度[1]。

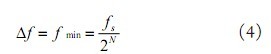

DDS输出的信号频率可以由下式给定:

其中:为参考时钟, 为信号频率分辨率,为输出信号频率, 为频率控制字, 为相位累加器的位数。可见,可以通过设定相位累加器的位数、频率控制字和系统参考时钟的值,就可以产生任意信号频率的输出[2]。

可以看出,当 时,可得DDS的最低输出频率即此DDS的频率分辨率为:

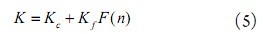

利用DDS实现调频,就是要使信号合成器输出信号的频率随着调制信号的幅度大小线性变化,瞬时频率的变化可以转化为对频率控制字的改变的控制[3]。假设调制信号经ADC转换为B位数字信号,为满足调制频偏要求,需在MCU内与一可调的调制常数相乘,乘积作为调制信号的频率控制字;再假设载波频率控制字为 ,则调频波的频率控制字为:

代入(1)式得调频波信号的瞬时频率序列:

考虑到相位累加器的积分器作用,假设波形存储器存储的为余弦波,则DDS输出的调频信号序列为:

再将调频信号序列 通过数模转换器和低通滤波器后,得到的模拟信号就是直接数字合成的调频信号。

硬件实现

由于采用全数字结构,DDS输出信号的频带受器件水平的限制,一般在几百兆以内。在本系统中,为了达到设计指标要求的100 ~ 400MHz的调制频段要求,综合考虑DDS芯片的技术水平以及成本问题,我们采用双通道DDS与混频器相结合的方案来提高调频信号的工作频段,这样每个通道的最大输出频率只需达到200MHz。向双通道DDS的两个通道送入相同的调频波频率控制字,则两个通道DDS-1和DDS-2产生完全同步的载波为的调频信号序列,再将调频信号序列分别通过D/A转换器和低通滤波器后混频,去掉直流成分,得到的模拟信号就是载波频率为的调频信号。系统的硬件结构原理如图1所示 。

信号发生模块

信号发生模块主要由DDS芯片组成,这里选用美国ADI公司的双通道直接数字频率合成器AD9958,最高采样频率可达 500 MSPS。它有两个DDS核,能够提供两个内部同步、独立编程同步输出通道,在系统时钟工作在500 MHz时,输出频率可控制范围可以达到0 ~ 200 MHz[4],可以满足系统设计的要求。

AD9958有4种工作模式,分别为单频模式、调制模式、线性扫描模式和幅度输出控制模式。其中单频模式是芯片服务后默认的工作模式,在此模式下输出是某一单调频率、幅度和初始相位的正弦波[5]。本系统中AD9958采用的就是单频模式,在这种工作模式下,两个DDS通道共享一个公共地址,频率控制字地址是寄存器(0x04),通过改变频率控制字,可以很方便的改变输出频率,结合通道选择控制字,两个通道可以独立输出互不相关的两路正弦波,控制功能由MCU完成。

由于DDS的输出最大频率受奈奎斯特抽样定理的限制,所以有,此时,考虑到器件因素,在实际使用中一般取。本系统中,外部参考时钟采用50M高稳晶振,DDS芯片时钟倍频器设置倍率为10,使系统时钟达到500 MHz。从而使每个通道可保证信号质量的最高输出频率达到200 MHz。

控制模块

控制模块的功能主要由MCU芯片组成,MCU内部集成丰富的外围设备,具有卓越的处理能力,应用MCU完成外围电路,可以使得整个系统结构简单,使用方便。在本系统中,MCU作为核心控制模块完成调制信号频率控制字的获取和载波频率控制字的接收以及对DDS的控制。

调制信号频率控制字:本系统通过MCU芯片集成的ADC完成调制信号频率控制字的获龋根据实际需要,本系统的调制信号为语音信号,频率集中在50 ~ 3400 Hz。根据奈奎斯特采样定理,ADC采样频率应不小于6.4 kHz,,考虑到高速密集采样可以减少频偏偏差,因此设定ADC采样频率为100 kHz。

- 一种基于AD9857的信号发生器的设计(09-07)

- 基于ML2035的简易正弦信号发生器(11-01)

- 基于SPMC75系列单片机的高性能三相变频电源(05-03)

- 基于AT89C52单片机的超低频信号发生器设计(06-01)

- 基于AD9957的USB侧音测距信号发生器设计(10-09)

- 可调电阻在稳压器温度漂移补偿中的设计(02-01)