多模多制式调制信号发生技术

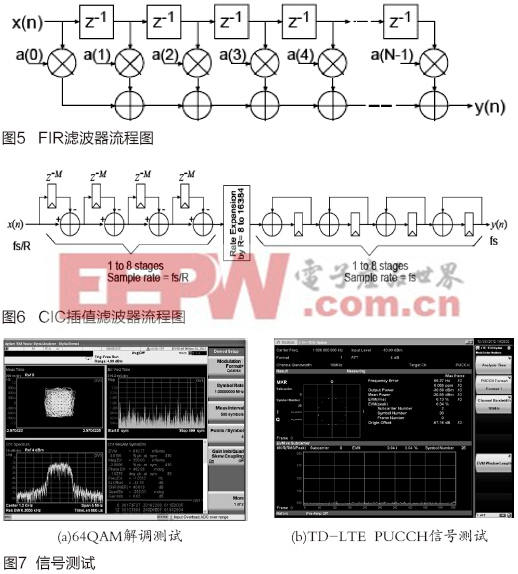

摘要:随着通信行业以及数字技术的不断发展,市场上经常需要多模通信信号或多制式数字调制信号发生器,本文介绍了采用软件无线电思想,基于“DDR2+FPGA+DAC+DDS+宽带调制器”的硬件结构的信号发生装置,实现了TD-SCDMA、WCDMA、TD-LTE、FDD-LTE等多模信号以及BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK等数字调制信号的发生,能很好满足现代信号模拟的实际需求。

1 引言

本设计针对市场的实际需求以及多模通信信号和多制式数字调制信号的特点,设计了以FPGA为主,“DDR2+FPGA+DAC+DDS+宽带调制器”为硬件架构的多模多制式通信矢量信号发生装置,利用FPGA可编程的特点,在尽量简化硬件设计的情况下,可以发射TD-SCDMA、WCDMA、TD-LTE、FDD-LTE等多模信号,发射BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK等多调制格式数字调制信号,并可以将用户数据灌入DDR2,根据用户实际需要发出,实现复杂信号模拟的功能。

2 设计目的

(1)多模通信信号:GSM/TD-SCDMA/WCDMA/TD-LTE/FDD-LTE等通信制式非信令信号。

(2)多制式调制信号:

● 调制格式:BPSK、QPSK、OQPSK、DQPSK、8PSK、16QAM、32QAM、64QAM、2FSK、4FSK、GMSK;

● 码元速率:2ksps~40Msps;

● 滤波类型RC、RRC、GAUSS;

● α因子/bt:0.2~1。

(3)用户数据发射。

(4)将上述信号调制到相应的载波上。

3 硬件设计实现

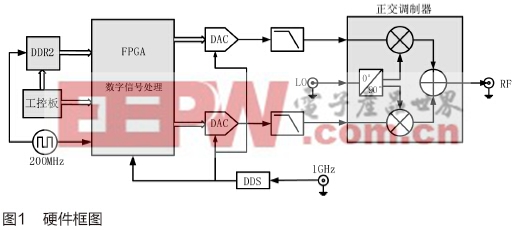

随着FPGA器件的快速发展,其高速大容量可编程的特点使其得到广泛应用,对多模多制式的设计需求需要选用FPGA进行设计,它主要完成数字信号处理工作。另外,由于TD-LTE、FDD-LTE的高数据量高速的要求,需要DDR2作为多模信号或用户数据的存储介质。在基带信号发生后,还需要将其DAC转换后用宽带正交调制器调制到各自载波上发射。另外,多模多制式信号的发生需要不同码元速率的设计,需要选用DDS分频出高分辨率可变时钟。所以该设计选用“DDR2+FPGA+DAC+DDS+宽带调制器”硬件架构,其框图如图1。

4 FPGA设计实现

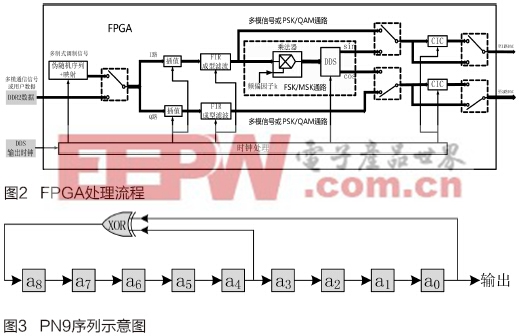

该设计的重点是对多模多制式调制信号进行数字信号处理,由FPGA完成,包括多模信号或用户数据的插值、FIR成型滤波、CIC插值等处理;以及多制式信号的伪随机信号产生、映射、插值、FIR成型滤波、频偏系数生成、DDS及CIC插值等处理。FPGA处理流程见图2。

PN码产生单元主要在时钟的作用下可以不断地产生原始的二进制伪随机序列,然后将产生的伪随机序列进行编码及映射,以QPSK为例,每两个二进制编码构成一个码元,即为{(00),(01),(10),(11)}四种状态,再映射为星座图上的相位点,如IQ两路幅度分别用9位补码表示,则为hex{(1ff1ff),(1ff0ff),(0ff1ff),(0ff0ff)},用IQ的幅值来表示信号的矢量位置。QPSK星座图见图4。

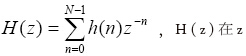

由于映射产生的是矩形脉冲信号,信号幅度的突变也会使其占用的频带很宽,不利于传输,造成符号间干扰,导致接收机在检测一个符号时发生错误的概率增大,需要设计脉冲成形滤波器,而各种滤波器可以通过有限脉冲响应数字FIR滤波器来实现,因为FIR滤波器有两大优点:

(1)单位脉冲响应h(n)有限长,长度为N的h(n)系统函数 ,H(z)在z平面有(N-1)个零点,原点z=0是(N-1)阶重极点而无其它极点,因而是稳定的;

,H(z)在z平面有(N-1)个零点,原点z=0是(N-1)阶重极点而无其它极点,因而是稳定的;

(2)在满足一定条件下(单位脉冲响应奇对称或偶对称),保证严格的线性相位。

它的基本算法是一种乘法-累加运算,即不断地输入样本x(n),经过z-1延时后,再进行乘法-累加,最后输出滤波结果y(n)。其实现流程和输出表达式如下所示。

式中,ai为滤波因子;x(n)表示滤波器在n时刻的输入;y(n)为n时刻的输出。

由图6可知FIR滤波器主要由一些延时器、乘法器和加法器等组成,其频响的调整由滤波因子来控制。滤波因子可以通过对滤波器频响采样后经过反傅立叶变换来得到,滤波因子的物理意义是滤波器频响在时域上的反映,在该设计中可以利用MATLAB进行仿真,得到各种滤波类型(RC、RRC、GAUSS)、不同滚降系数(0.20-1.00)的滤波因子。滤波因子可以根据用户需求和通信制式选用。

在该设计中,基带信号的码元速率变化范围很大,如果将成形后的数据直接输出给D/A转换器,输出信号必然带有D/A工作时钟信号,而我们设计的基带带宽大,要滤除时钟但不影响信号,模拟低通滤波器将很难设计,所以我们增添了CIC插补滤波模块来提高DAC的采样时钟,CIC滤波器可以用来实现抽取器和内插器,它具有结构简单、规整以及需要的存储量小的优点。由于它不

多模 调制信号 FPGA DDS FIR滤波器 201504 相关文章:

- 如何为多种无线标准设计可编程基带设备(05-19)

- 多模式开关电源控制芯片的低功耗设计与实现(01-16)

- 多模功放技术应对音频设计面临的诸多挑战(01-18)

- 利用信号调节器的抗混淆滤波器,实现混合信号、多模态传感器调节(10-16)

- 携手独立型芯片商 高通大啖多模无线充电商机(10-16)

- 基于AXIe中PCIe高带宽及多模块的高速同步图形传输系统(12-21)