基于DSP的机器人视觉伺服系统研究与设计

时间:11-27

来源:互联网

点击:

1. 引言

机器人视觉伺服系统是机器人领域中的重要研究方向,起源于80年代初,随着计算机技术、图像处理技术、控制理论的发展,取得了很大进步,有一些系统已投入使用。视觉伺服跟通常所说的机器视觉有所不同,视觉伺服是利用机器视觉的原理,进行图像的自动获取分析,从直接得到的图像处理反馈信息中,快速进行图像处理,在尽量短的时间内给出反馈信号,构成机器人的位置闭环控制,实现对机器人的控制。正是由于系统以实现某种控制为目的,所以视觉伺服系统中的图像处理过程必须快速准确。本文主要针对机器人视觉伺服系统要求快速准确的特点,为满足项目研究的需要,讨论研究了基于DSP的图像反馈机器人视觉伺服技术。

2 . 系统工作原理及硬件构成

基于图像的视觉伺服直接计算图像误差,产生控制信号,并变换到机器人运动空间,驱动机械手,完成伺服任务。该方法对标定误差和空间模型误差不敏感。

对于机器人视觉伺服系统,实时性问题一直是一个难以解决的重要问题。图像采集速度较低以及图像处理需要较长时间会给系统带来明显的时滞;此外视觉信息的引入也明显增大了系统的计算量。而图像处理速度是影响视觉伺服系统实时性的主要瓶颈之一。

实时图像处理设计的难点是如何在有限的时间内完成对大量图像数据的处理。从人的视觉理论分析,只有图像处理系统的处理速度达每秒25帧以上时才能达到实时的效果,即要求实时图像处理系统必须在40ms内完成对一帧l图像的运算处理,才能保证图像的实时性。为了达到该处理速度,我们采用了基于DSP的图像视觉伺服方式,其结构如图1所示。

图1 基于DSP的图像反馈机器人视觉伺服结构图

2.1 WTC6201PA板简介

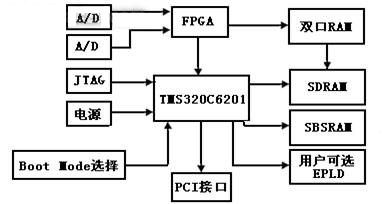

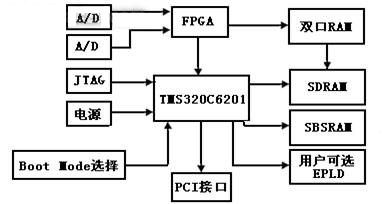

本文选用了闻亭公司的WTC6201PA板,其板上硬件组成如图2所示。

图2 WTC6201PA板硬件组成

WTC6201PA板属于EVM板中的一种,它采用了TI公司的DSP器件TMS320C6201芯片。TMS320C6201芯片的最高时钟频率为200MHZ,每个时钟周期最多可以执行8条指令,从而实现16000MIPS的定点运算能力,它具有如下主要特点:

· 采用了修正的哈佛总线结构,独立的程序总线、数据总线和DMA总线使得取指、读写数据和DMA操作可以并行。

· 采用流水线处理,使两个或多个不同的操作可以重叠执行,提高了程序执行速度。

· 具有高性能的外部存储器扩展接口EMIF,可以直接与同步突发静态存储器SBSRAM、同步动态存储器SDRAM连接,用于大容量、高速存储;还包括直接异步存储器接口,可与静态存储器SRAM、只读存储器EPROM连接,用于小容量的数据存储和程序存储;芯片内部集成的64K程序存储器可配置成CASHE,以提高程序执行效率。

· 16位主机口能够和其它CPU的存储区以及外围电路进行通信。且多通道DMA控制器可在没有CPU参与的情况下完成映射存储空间中的数据搬移,从而减轻CPU的工作量。

同时板上配置了高速同步存储器SBSRAM(128K×32Bit)和SDRAM(4M×32bit),两路A/D转换器,大容量的FPGA器件和外部I/O接口,板上还提供了一个McBSP接口,兼容5V TTL电平,方便用户与外部系统通信。WT6201PA板满足PCI Local Bus Revision 2.1 协议,主机可访问DSP的所有资源,用户可通过主机加载程序。WTC6201PA板提供了Win98和NT下的驱动软件及DSP的应用软件(APIs),利用这个硬件平台和底层软件库,用户可以很容易的进行软件开发。

2.2 系统硬件实现

我们选用了WTC6201PA板上的TMS320C6201芯片、FPGA、SBSRAM、SDRAM、双口RAM、PCI总线、JTAG接口等硬件资源作为视觉图像处理单元,和PC主控机、图像采集卡、CCD摄像机和机器人控制系统组成系统,原理框图如图3所示。

图3 系统原理框图

系统工作过程如下:

CCD摄像机输出标准制式的全电视信号,其中包含着图像信号、复合同步信号、行、场消隐信号、槽脉冲和前后均衡脉冲等七种信号。本系统采用了北京大恒公司的DH-PCI-H图像采集卡来实现视频信号的预处理。CCD摄像机将视频数据输入到图像采集卡,图像采集卡按照设定的窗口位置、大小和方式采集视频数据,采集的数据存储在计算机的内存中。图像传输由图像卡控制的,无需CPU参与,图像传输速度可达40MB/S。

设置图像采集卡的采集方式是25帧/s连续采集,则采集一帧的时间为40ms,每一帧图像由奇偶两场组成,场频为50HZ,即一场扫描时间为20ms。图像采集大小为512×512像素,量化为8bit,256灰度级,则一帧图像的数据量为512×512×8bit=256KB。图像数据存储方式为隔行存放,即奇、偶场的图像数据交叉存放,组成一帧完整图像函数。

C6201由BOOTMODE[4:0]设置芯片的自举方式,加载过程采用主机(HPI)引导方式。外部主机通过主机口初始化CPU的存储空间,主机完成所有的初始化后,将主机口控制寄存器中的DSPINT位设置为1,结束引导过程。CPU退出复位状态,开始执行地址0处的指令。

系统上电后,主机经HPI口对系统初始化,主要完成对各寄存器的设置,包括EMIF、中断、DMA等相关的寄存器初始化操作等。主机向HPI控制寄存器的DSPINT位写1触发DSP运行,系统进入等待状态。CCD摄像机实时采集图像,经图像采集卡处理后存储到主机内存。PC机内存缓冲区一帧存满,向DSP发中断信号,DSP应答后,通过PCI总线将图像数据从主机内存经HPI口传输到WTC6201PA板片外SDRAM。DSP控制波门范围内图像数据以DMA方式传输到内部数据存储器。由于DSP为指令结构处理芯片,具有可编程性好、可以处理大量复杂指令(由程序RAM地址空间的大小决定)等优点,但相对FPGA而言其处理速度比较慢;而FPGA为可编程逻辑器件,具有很强的细粒度并行处理和多级流水线处理能力,但其内部有限的逻辑资源使之不适合实现复杂逻辑运算。因此我们采用FPGA作为协处理器来完成底层操作,再由DSP完成高层操作,两种操作可以采用流水线的方式并行运行,共同完成高速图像处理。从FPGA到DSP之间的图像数据传输使用双端口RAM。处理完一帧图像后,DSP向主机发信息,主机应答后,将图像处理结果经PCI总线传输至PC机内存,PC机再将位置偏差数据信号送至伺服控制系统,完成伺服任务。

机器人视觉伺服系统是机器人领域中的重要研究方向,起源于80年代初,随着计算机技术、图像处理技术、控制理论的发展,取得了很大进步,有一些系统已投入使用。视觉伺服跟通常所说的机器视觉有所不同,视觉伺服是利用机器视觉的原理,进行图像的自动获取分析,从直接得到的图像处理反馈信息中,快速进行图像处理,在尽量短的时间内给出反馈信号,构成机器人的位置闭环控制,实现对机器人的控制。正是由于系统以实现某种控制为目的,所以视觉伺服系统中的图像处理过程必须快速准确。本文主要针对机器人视觉伺服系统要求快速准确的特点,为满足项目研究的需要,讨论研究了基于DSP的图像反馈机器人视觉伺服技术。

2 . 系统工作原理及硬件构成

基于图像的视觉伺服直接计算图像误差,产生控制信号,并变换到机器人运动空间,驱动机械手,完成伺服任务。该方法对标定误差和空间模型误差不敏感。

对于机器人视觉伺服系统,实时性问题一直是一个难以解决的重要问题。图像采集速度较低以及图像处理需要较长时间会给系统带来明显的时滞;此外视觉信息的引入也明显增大了系统的计算量。而图像处理速度是影响视觉伺服系统实时性的主要瓶颈之一。

实时图像处理设计的难点是如何在有限的时间内完成对大量图像数据的处理。从人的视觉理论分析,只有图像处理系统的处理速度达每秒25帧以上时才能达到实时的效果,即要求实时图像处理系统必须在40ms内完成对一帧l图像的运算处理,才能保证图像的实时性。为了达到该处理速度,我们采用了基于DSP的图像视觉伺服方式,其结构如图1所示。

图1 基于DSP的图像反馈机器人视觉伺服结构图

2.1 WTC6201PA板简介

本文选用了闻亭公司的WTC6201PA板,其板上硬件组成如图2所示。

图2 WTC6201PA板硬件组成

WTC6201PA板属于EVM板中的一种,它采用了TI公司的DSP器件TMS320C6201芯片。TMS320C6201芯片的最高时钟频率为200MHZ,每个时钟周期最多可以执行8条指令,从而实现16000MIPS的定点运算能力,它具有如下主要特点:

· 采用了修正的哈佛总线结构,独立的程序总线、数据总线和DMA总线使得取指、读写数据和DMA操作可以并行。

· 采用流水线处理,使两个或多个不同的操作可以重叠执行,提高了程序执行速度。

· 具有高性能的外部存储器扩展接口EMIF,可以直接与同步突发静态存储器SBSRAM、同步动态存储器SDRAM连接,用于大容量、高速存储;还包括直接异步存储器接口,可与静态存储器SRAM、只读存储器EPROM连接,用于小容量的数据存储和程序存储;芯片内部集成的64K程序存储器可配置成CASHE,以提高程序执行效率。

· 16位主机口能够和其它CPU的存储区以及外围电路进行通信。且多通道DMA控制器可在没有CPU参与的情况下完成映射存储空间中的数据搬移,从而减轻CPU的工作量。

同时板上配置了高速同步存储器SBSRAM(128K×32Bit)和SDRAM(4M×32bit),两路A/D转换器,大容量的FPGA器件和外部I/O接口,板上还提供了一个McBSP接口,兼容5V TTL电平,方便用户与外部系统通信。WT6201PA板满足PCI Local Bus Revision 2.1 协议,主机可访问DSP的所有资源,用户可通过主机加载程序。WTC6201PA板提供了Win98和NT下的驱动软件及DSP的应用软件(APIs),利用这个硬件平台和底层软件库,用户可以很容易的进行软件开发。

2.2 系统硬件实现

我们选用了WTC6201PA板上的TMS320C6201芯片、FPGA、SBSRAM、SDRAM、双口RAM、PCI总线、JTAG接口等硬件资源作为视觉图像处理单元,和PC主控机、图像采集卡、CCD摄像机和机器人控制系统组成系统,原理框图如图3所示。

图3 系统原理框图

系统工作过程如下:

CCD摄像机输出标准制式的全电视信号,其中包含着图像信号、复合同步信号、行、场消隐信号、槽脉冲和前后均衡脉冲等七种信号。本系统采用了北京大恒公司的DH-PCI-H图像采集卡来实现视频信号的预处理。CCD摄像机将视频数据输入到图像采集卡,图像采集卡按照设定的窗口位置、大小和方式采集视频数据,采集的数据存储在计算机的内存中。图像传输由图像卡控制的,无需CPU参与,图像传输速度可达40MB/S。

设置图像采集卡的采集方式是25帧/s连续采集,则采集一帧的时间为40ms,每一帧图像由奇偶两场组成,场频为50HZ,即一场扫描时间为20ms。图像采集大小为512×512像素,量化为8bit,256灰度级,则一帧图像的数据量为512×512×8bit=256KB。图像数据存储方式为隔行存放,即奇、偶场的图像数据交叉存放,组成一帧完整图像函数。

C6201由BOOTMODE[4:0]设置芯片的自举方式,加载过程采用主机(HPI)引导方式。外部主机通过主机口初始化CPU的存储空间,主机完成所有的初始化后,将主机口控制寄存器中的DSPINT位设置为1,结束引导过程。CPU退出复位状态,开始执行地址0处的指令。

系统上电后,主机经HPI口对系统初始化,主要完成对各寄存器的设置,包括EMIF、中断、DMA等相关的寄存器初始化操作等。主机向HPI控制寄存器的DSPINT位写1触发DSP运行,系统进入等待状态。CCD摄像机实时采集图像,经图像采集卡处理后存储到主机内存。PC机内存缓冲区一帧存满,向DSP发中断信号,DSP应答后,通过PCI总线将图像数据从主机内存经HPI口传输到WTC6201PA板片外SDRAM。DSP控制波门范围内图像数据以DMA方式传输到内部数据存储器。由于DSP为指令结构处理芯片,具有可编程性好、可以处理大量复杂指令(由程序RAM地址空间的大小决定)等优点,但相对FPGA而言其处理速度比较慢;而FPGA为可编程逻辑器件,具有很强的细粒度并行处理和多级流水线处理能力,但其内部有限的逻辑资源使之不适合实现复杂逻辑运算。因此我们采用FPGA作为协处理器来完成底层操作,再由DSP完成高层操作,两种操作可以采用流水线的方式并行运行,共同完成高速图像处理。从FPGA到DSP之间的图像数据传输使用双端口RAM。处理完一帧图像后,DSP向主机发信息,主机应答后,将图像处理结果经PCI总线传输至PC机内存,PC机再将位置偏差数据信号送至伺服控制系统,完成伺服任务。

机器人 机器视觉 DSP MIPS 总线 电路 FPGA 神经网络 相关文章:

- 基于MSP430的自主式移动机器人设计与实现(06-12)

- 如何制作一个最简单的机器人(02-23)

- 机器人技术的新进展(02-23)

- CAN总线技术在工业码垛机器人控制系统中的应用研究(06-27)

- 制作机器人常用传感器盘点(02-23)

- 基于LabVIEW构建智能的移动机器人及无人驾驶车(10-27)