例说FPGA连载53:NAND Flash实例之Avalon-MM总线

input clk;

input reset_n;

input write_n;

input [ 31: 0] writedata;

wire clk_en;

reg data_out;

wire out_port;

wire read_mux_out;

wire [ 31: 0] readdata;

assign clk_en = 1;

//s1, which is an e_avalon_slave

assign read_mux_out = {1 {(address == 0)}} & data_out;

always @(posedge clk or negedge reset_n)

begin

if (reset_n == 0)

data_out <= 0;

else if (chipselect && ~write_n && (address == 0))

data_out <= writedata;

end

assign readdata = {32'b0 | read_mux_out};

assign out_port = data_out;

endmodule

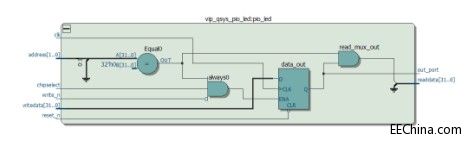

如图6.10所示,从工程的RTL视图里也可以看到PIO_LED外设的接口信号,和代码里的接口是一致的。

图6.10 PIO外设的RTL视图

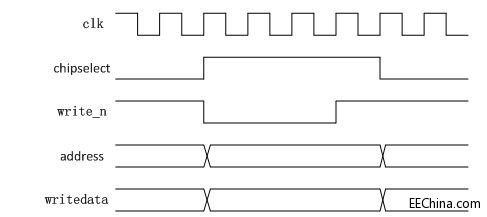

这些接口中,作为inputs的信号中,时钟信号clk、复位信号reset_n是由系统提供的。其他几个信号如地址信号address、片选信号chipselect、写选通信号write_n和写入数据writedata都是Avalon总线上的常用信号。简单的来看,使用这几个信号组成的Avalon总线接口写时序如图6.11所示。

图6.11 PIO外设的写时序波形

写选通信号和片选信号的有效时钟周期数也都是可变的,甚至地址和数据的有效时钟宽度也都是可调整的。由此足见Avalon接口的灵活性,尤其在开发者自己设计Avalon从机作为Qsys上的一个自定义组件时,我们更是可以根据从机的实际状况将各个接口信号的时序关系调整到一个最优的状态。

回过头来,再看前面给出的从机底层代码,用文字描述可能会显得比读代码更枯燥,因为波形都给出来了,有点基础的朋友恐怕都更愿意去对照着波形解读代码。这里的接口代码只是一种最简洁的写法,里面有一些技巧,我们可以模仿,但是不要把思路限制住,我们要活学活用,如此你才会逐渐发觉——设计原来如此简单。

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)