例说FPGA连载53:NAND Flash实例之Avalon-MM总线

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

话说Avalon-MM总线就好像一条康庄大道,而各个主机或是从机都是通过一条专用通道连接到这条主干线上。主机有访问各个从机的主动权,一个系统中的主机可以不止一个,CPU可以是主机,DMA也可以是。当CPU通过康庄大道访问从机A的时候,DMA也可以通过这条康庄大道访问从机A以外的其他从机,二者互不冲突。但是,如果CPU访问从机A,DMA也试图访问从机A,那么我们就发现最终通往从机A的那条“专用通道”就要抗议了,一山难容二虎啊。此时我们就必须考虑加入一些仲裁逻辑,可以让某个主机优先访问,也可以遵循“先来后到”的准则。

回到概念上来,Avalon-MM总线所针对的是主从连接、可以用地址进行访问的通信。对于很多嵌入式的软件工程师,他们潜意识里已经把这些复杂外设的驱动控制理解为对datasheet里那些大大小小的寄存器所对应的地址进行读读写写了。问题也的确这么简单,而Avalon-MM接口就是顺着大家的这种惯常思维(毕竟这已成为了一种标准了)应运而生。其实简单的Avalon-MM接口时序和前面介绍的INTEL接口或是MOTOROLA接口很是有几分相似。所以,大家也不用太恐惧,面对Avalon-MM我们有信心,不仅是弄懂它,更是要玩转它。

因为在实例就是要来做一个与NIOS II连接的Avalon-MM从机组件,所以我们会在实践中更深入的接触Avalon-MM这位漂亮的美眉(MM)。这里为了让大家对Avalon-MM总线的通信方式有一些直观的认识,就列举一个最简单的Avalon-MM主从工作机制进行讨论,也就是之前的例程我们使用GPIO配置为Output外设时的写操作。

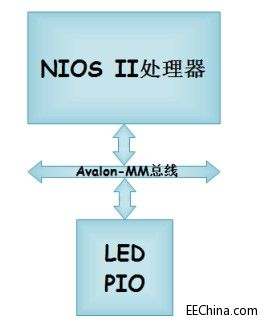

就拿第工程实例3的PIO_LED外设来看,我们可以先回顾一下当初定义这个外设的功能。无非就是一个1位输出的GPIO外设,当我们软件编程时往其对应地址写入数据值就可以控制LED引脚的输出电平状态。其硬件连接关系大体如图6.8所示。

图6.8 简单的NIOS II处理器与外设互联接口

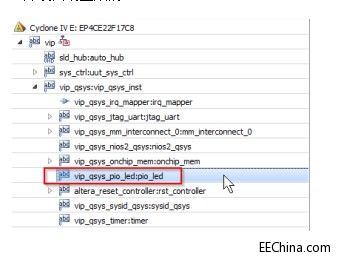

那么我们可能还会更关心这个硬件连接的具体实现细节,也就是Avalon-MM总结的控制时序。如图6.9所示,打开工程管理窗口中的pio_led模块代码,这个代码是根据我们在Qsys中配置的PIO_LED外设自动生成的。

图6.9 工程代码层次结构

PIO_LED的从机接口逻辑代码如下。

module vip_qsys_pio_led (

// inputs:

address,

chipselect,

clk,

reset_n,

write_n,

writedata,

// outputs:

out_port,

readdata

);

output out_port;

output [ 31: 0] readdata;

input [ 1: 0] address;

input chipselect;

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)