例说FPGA连载52:NAND Flash实例之总线的概念

其实上面提到的INTEL总线和MOTOROLA总线是CPU和外设数据交互的一种方式,在硬件工程师的板级设计中看得到固定信号连接的通信方式。而在我们后面将要重点讨论的这种CPU与外设的互连总线却是硬件工程师在PCB板上看不到的。也就是说,我们这里的外设不在“外”而在“内”,这些外设是集成在CPU内部的,而CPU内部的总线互连架构是板级设计的工程师们无法直观看到的。但是作为Qsys系统架构的工程师,我们就必须深入的研究这些互联总线的工作机理。毕竟,完全DIY出来的Qsys硬件系统中所有的组件都是我们根据系统需求精挑细选出来的,那么他们之间的衔接和数据交换也必须是我们能够去“设计”的一部分。

先不讨论在Altera的Qsys平台主流的Avalon总线,我们可以去研究一下ARM7系统中常见的内部系统总线是什么样的。如图6.6所示,这是NXP公司推出的一款内嵌ARM7TDMI-S内核的控制器内部功能框图。

图6.6 ARM芯片内部功能框图

在这个框图里,我们不是很关心它都集成了哪些外设,而是要看看它的处理器内核与其他外设以及外设与外设之间是如何互连的。简单的看,从内核引出的两条总线分别是Local bus和Advanced high-performance bus(AHB),Local bus即本地总线上挂靠的都是一些实时性要求最高、数据吞吐量最大的“外设”。毫无疑问,在一个系统中,这种实时性最高、数据吞吐量最大的“外设”非存储器莫属,因为程序运行、数据变量读写都要频繁的访问ROM或RAM。除此之外,我们也看到有一个高速GPIO模块也“运行”在这条“高速公路”上,该款芯片特别的增强了GPIO的性能,那一定是为满足一些特定的应用需求而设计的。除了存储器,其实这条高速总线是可以挂靠任何符合总线通信规范的外设组件的,但是一旦这条“高速公路”的“车”多了,就不可避免的发生拥堵,那么所谓“高速”就名不副其实了。

那怎么办,系统还有一大堆外设需要挂靠呢?不是还有一条AHB总线吗,这也是一条高性能总线,虽然可能和本地总线比还是要差点。这条总线上挂着一个中断向量控制器(VECTORED INTERRUPT CONTROLLER)和一个桥(AHB TO APB BRIDGE)。无疑的,系统的中断需要第一时间得到响应,因此它也就被挂在离处理器内核最近的总线上。最后来看那个AHB2APB桥,我们知道一般的嵌入式外设速度都不高,因此在这个系统内部,就把所有余下的外设组件都挂在了一条叫做APB的总线上,而这条APB总线最终也是需要挂在与CPU直接相连的AHB总线上。那么,AHB2APB桥所做的就是连接APB总线和AHB总线,并且它还要像CPU本身一样作为APB总线的主机,来统管各个外设。

费了这么些篇幅,好歹我们讲到CPU内部的片上总线了。除了ARM7上流行的AMBA总线外,还有Silicore的WISHBONE总线(很多开源设计都采用此总线)、IBM的CoreConnect总线,然后就是Altera的Avalon总线。不同总线各有特点,适用范围也有不同。Avalon总线就是Altera公司主推的应用于其软核处理器NIOS II上的总线,主要包括Avalon-MM总线和Avalon-ST总线,下面我们就去认识他们。

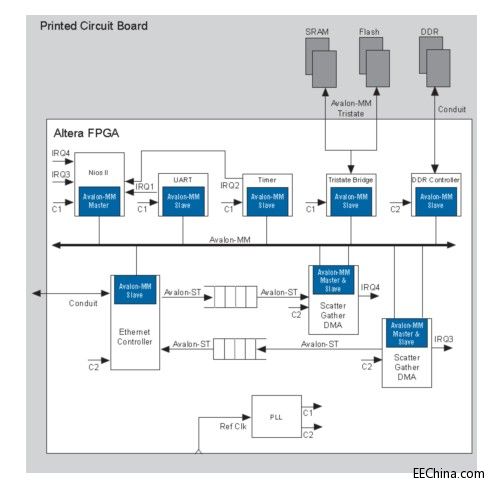

基于NIOS II处理器的片内系统互连主要靠的就是Avalon-MM总线和Avalon-ST总线。如图6.7所示,一个典型的NIOS II系统,NIOS II处理器和各外设之间通过Avalon-MM总线进行交互,而外设之间的点到点数据传输则可以通过Avalon-ST总线来完成。Avalon-MM (Avalon Memory Mapped Interface)总线是一种基于地址读写的主从互连的机制。Avalon-ST(Avalon Streaming Interface)总线主要应用于单向数据流传输,可以完成点到点的大数据量吞吐。另外也略带提一下,在Avalon总线规范里,还有Avalon-MM Tristate和Conduit接口。前者主要是Avalon-MM的一个扩展,也可以理解为它是Avalon-MM的一个“集线器”,对一个Avalon-MM从机进行复用,这样做的好处是减少从机接口的数量,用一套总线信号就可以挂接多个从机。比如在接口信号的数量紧张时,尤其是连接到FPGA外部引脚上的多个存储器(如图中的SRAM和FLASH),此时就可以复用到一个Avalon-MM Tristate接口上。而Conduit接口则是Avalon-MM从机引出的可以连接到FPGA其它逻辑模块或是FPGA外部引脚上的信号接口。

图6.7 典型NIOS II系统

FPGA 总线 嵌入式 GPS 电子 电路 USB 单片机 硬件工程师 PCB Altera ARM NXP 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)