例说FPGA连载52:NAND Flash实例之总线的概念

特权同学,版权所有

配套例程和更多资料下载链接:

http://pan.baidu.com/s/1c0nf6Qc

关于总线,比较官方的说法是:总线(Bus)是计算机各种功能部件之间传送信息的公共通信干线。说到计算机,大家不要下意识的就以为只是特指每天我们都要面对的电脑。比较高端的计算机,火箭用的叫箭载计算机,卫星上用的叫星载计算机;稍微逊色一点的,工业上用的叫工控机,我们家里用的叫PC机、笔记本;而嵌入式用的计算机更是数不胜数了,PDD、GPS和手机,MP3、MP4和电纸书,电梯、冰箱和微波炉的电子控制部分,细细找找,发现生活中凡是涉及电的还真没有一样离得开“微电”的控制。提到控制,那么肯定或大或小有个CPU,一旦和CPU搭上边好歹也要算个小型计算机了。计算机不仅有CPU,还需要有各种外设配合CPU与外界通信,那么CPU与外设之间的通信靠什么,总线?YES,虽然不是每一个系统中都要有总线,但凡大一点的系统都会有总线,因为总线能够很好的衔接管理各个外设与CPU之间的通信,能够简化硬件电路设计和系统结构。所以,废话了这么多,你该领悟总线很重要了吧。

光说重要你肯定感觉不过瘾,要打破沙锅问到底,总线到底如何工作?如何连接CPU和外设?

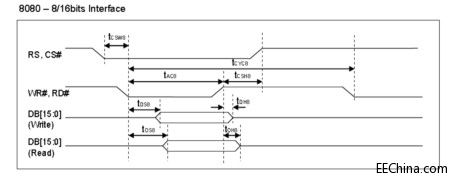

广义上来说,任何衔接多个外设甚至是多个相同外设的一组信号都可以称为“总线”,比如CAN总线、USB总线、IIC总线等等。但在这里所论述的总线,主要是针对CPU与外设之间的总线。在嵌入式系统应用中,最简单也许大家都接触过的有INTEL总线和MOTOROLA总线。这两类总线最初应用于INTEL和MOTOROLA 两家公司生产的处理器,最为典型的是早期的PC系列处理器如INTEL的8086和MOTOROLA的MC6800,以至于后来的很多单片机乃至外设芯片的并口通信都能够兼容这两种模式的总线。为了更好的理解总线的概念,不妨让我们看看这两种总线的工作机制。如图6.4和图6.5所示,是一颗支持与单片机的INTEL和MOROROLA接口连接的芯片的读写时序图。习惯上,大家一谈到8080总线就认定是INTEL总线,6800总线也就是MOTOROLA总线。从这两个时序图上,我们看到的区别恐怕主要是读写选通的区别。INTEL总线分别使用读选通信号RD#和写选通信号WR#两个信号的低电平状态来表示当前处于读或写选通状态。而MOTOROLA总线则只使用一条RW#信号来表示当前的读写状态,当总线选通期间,若RW#为高电平则表示读状态,低电平则为写状态。除此以外,规范的INTEL总线和MOTOROLA总线在地址和数据总线的使用上也是有所区别的。

另外,我们需要从这两个时序图中看到一个基本的“总线雏形”。也就是说,一条规范的总线,无外乎控制信号(有时候我们也习惯的称之为控制总线,但是此总线非彼总线,大家注意区分)、地址信号、数据信号这三类信号组成。如INTEL总线的控制信号主要有片选信号CS#、写选通信号WR#、读选通RD#和地址/数据选择信号RS,他们的功能就是用于指示当前的总线处于怎样的状态——是正在读取数据、正在写入数据、正在写入地址还是闲置中。他们的地址信号和数据信号是复用(很多总线的地址和数据信号不是复用的,如Avalon总线就是分离的)的,即时序图中的DB[15:0]。在一次读写操作中,如果RS为高电平,则表示当前操作为命令的读或写;如果RS低高电平,则表示当前操作为数据的读或写。

图6.4 INTEL总线时序图

图6.5 MOTOROLA总线时序图

INTEL总线和MOTOROLA总线在嵌入式系统中仍大行其道,甚至于随处可见,不信你可以随便download个芯片的datasheet看看。对我们的学习而言,认识一条总线的目的不在于领会总线本身的工作机制而已,尤其是要成为一名FPGA工程师,我们常常要和底层的硬件打交道。因此,我们学习的最终目的是学以致用。在笔者所著的《深入浅出玩转FPGA》笔记8的“单向控制信号检测”小节里就讲述了一种用FPGA逻辑来设计INTEL/MOTOROLA总线的从机。

其实上面提到的INTEL总线和MOTOROLA总线是CPU和外设数据交互的一种方式,在硬件工程师的板级设计中看得到固定信号连接的通信方式。而在我们后面将要重点讨论的这种CPU与外设的互连总线却是硬件工程师在PCB板上看不到的。也就是说,我们这里的外设不在“外”而在“内”,这些外设是集成在CPU内部的,而CPU内部的总线互连架构是板级设计的工程师们无法直观看到的。但是作为Qsys系统架构的工程师,我们就必须深入的研究这些互联总线的工作机理。毕竟,完全DIY出来的Qsys硬件系统中所有的组件都是我们根据系统需求精挑细选出来的,那么他们

FPGA 总线 嵌入式 GPS 电子 电路 USB 单片机 硬件工程师 PCB Altera ARM NXP 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于Virtex-5 FPGA设计Gbps无线通信基站(05-12)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于ARM的嵌入式系统中从串配置FPGA的实现(06-09)

- 采用EEPROM对大容量FPGA芯片数据实现串行加载(03-18)

- 赛灵思:可编程逻辑不仅已是大势所趋,而且势不可挡(07-24)