ISE时序约束笔记5——Timing Groups and OFFSET Constraints

时间:02-19

来源:互联网

点击:

特定路径时序约束

使用全局时序约束(PERIOD,OFFSET,PAD-TO-PDA)将约束整个设计

仅仅使用全局约束通常会导致过约束

——约束过紧

——编译时间延长并且可能阻止实现时序目标

——通过综合工具或者映射后时序报告重新审视性能评估

特定路径约束能够覆盖全局时序约束在特定路径上的约束

——这就允许设计者放宽特定路径的时序要求

更多关于特定路径约束

你的设计器件的内部面积将会从特定路径约束收益

1. 多周期路径Multi-cycle paths

2. 跨时钟域路径

3. 双向总线

4. I/O时序

特定路径约束应该由你的性能目标来界定,不能够不加限制的随意放置

全局约束回顾

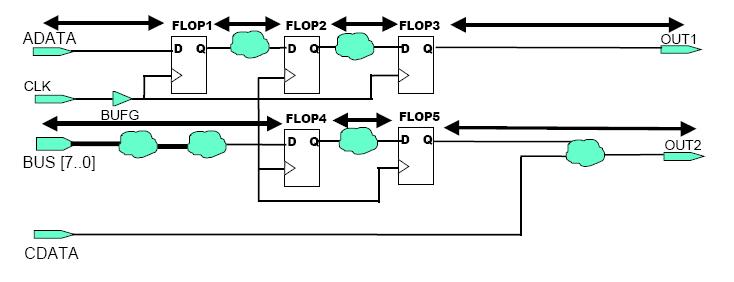

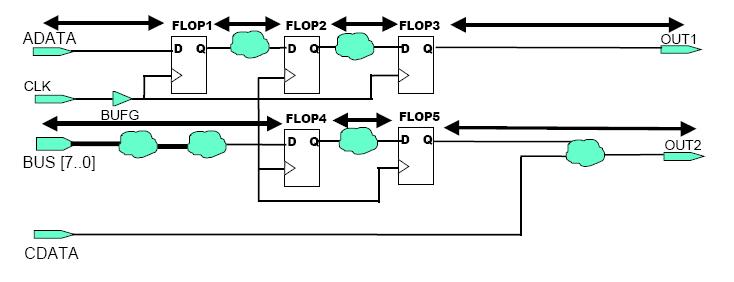

使用全局PERIOD,OFFSET IN和OFFSET OUT约束将约束所有以下的路径

这使得控制设计的总体性能更加容易

特定路径约束实例

一条特定路径约束对于路径本身的优化微乎其微

这有助于你更好的控制设计性能,并带给执行工具更大的灵活性以达到你的性能和使用要求

生成特定路径约束需要两个步骤:

1. 多个有共同时序要求的特定路径终点生成一个groups

2. 关联两个groups,指定它们的特定路径的时序要求

生成终点路径的Groups

特定路径时序约束在终点路径较好的分组后会更加高效——否则,约束一个大的工程将极其耗时耗力。

约束编辑有助于你更容易的进行路径终点(pads, flip-flops, latches, and RAMs)进行Groups分组。

使用约束编辑器,终点路径的分组有以下选项:

– Group by nets

– Group by instance name

– Group by hierarchy

– Group by output net name

– Timing THRU Points option

– Group by clock edge

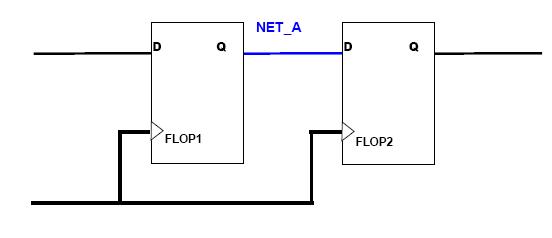

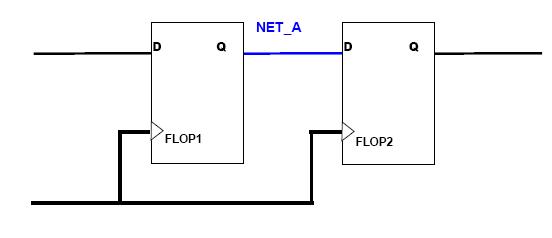

Nets 分组与output net name分组对比

由net分组的 “NET_A”将生成一个只包含FLOP2的group

——Group包含选择网络所驱动的寄存器

由output net name分组的“NET_A”将生成一个只包含FLOP1的group

——Group包含选择网络的源寄存器

使用全局时序约束(PERIOD,OFFSET,PAD-TO-PDA)将约束整个设计

仅仅使用全局约束通常会导致过约束

——约束过紧

——编译时间延长并且可能阻止实现时序目标

——通过综合工具或者映射后时序报告重新审视性能评估

特定路径约束能够覆盖全局时序约束在特定路径上的约束

——这就允许设计者放宽特定路径的时序要求

更多关于特定路径约束

你的设计器件的内部面积将会从特定路径约束收益

1. 多周期路径Multi-cycle paths

2. 跨时钟域路径

3. 双向总线

4. I/O时序

特定路径约束应该由你的性能目标来界定,不能够不加限制的随意放置

全局约束回顾

使用全局PERIOD,OFFSET IN和OFFSET OUT约束将约束所有以下的路径

这使得控制设计的总体性能更加容易

特定路径约束实例

一条特定路径约束对于路径本身的优化微乎其微

这有助于你更好的控制设计性能,并带给执行工具更大的灵活性以达到你的性能和使用要求

生成特定路径约束需要两个步骤:

1. 多个有共同时序要求的特定路径终点生成一个groups

2. 关联两个groups,指定它们的特定路径的时序要求

生成终点路径的Groups

特定路径时序约束在终点路径较好的分组后会更加高效——否则,约束一个大的工程将极其耗时耗力。

约束编辑有助于你更容易的进行路径终点(pads, flip-flops, latches, and RAMs)进行Groups分组。

使用约束编辑器,终点路径的分组有以下选项:

– Group by nets

– Group by instance name

– Group by hierarchy

– Group by output net name

– Timing THRU Points option

– Group by clock edge

Nets 分组与output net name分组对比

由net分组的 “NET_A”将生成一个只包含FLOP2的group

——Group包含选择网络所驱动的寄存器

由output net name分组的“NET_A”将生成一个只包含FLOP1的group

——Group包含选择网络的源寄存器

总线 相关文章:

- 基于FPGA的片上系统的无线保密通信终端(02-16)

- 基于FPGA的DVI/HDMI接口实现(05-13)

- 基于PLB总线的H.264整数变换量化软核的设计(03-20)

- FPGA 重复配置和测试的实现(08-14)

- 经I/O优化的FPGA(04-23)

- 基于Actel FPGA的PWM IP的应用(09-17)