不同的verilog代码风格看RTL视图之三

时间:02-19

来源:互联网

点击:

我们来做一个4选一的Mux的实验,首先是利用if…else语句来做,如下。

(由输入xsel来选择输出的路数xin0,xin1,xin2,xin3其一,输出yout)

Ex3:

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

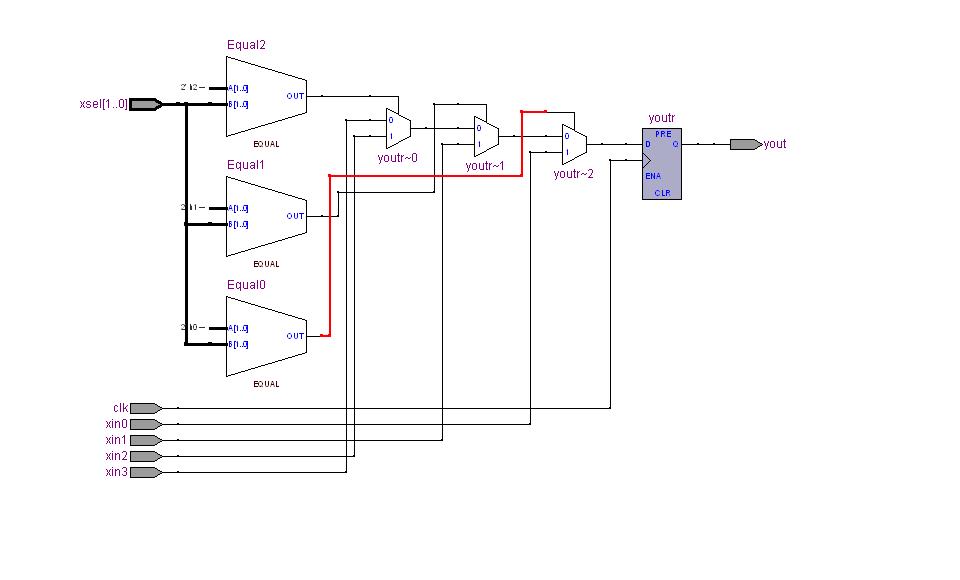

if(xsel == 2'b00) youtr RTL视图如下:

上面的视图里,可以看出有三个等于比较器,然后在触发器前会有三个2选1的选择器。和我们的代码是一样的,第一个if语句的优先级是最高的(这里所谓的优先级最高不是软件意义上的高优先级,由于HDL设计的并行性,判断语句综合后不是先后进行判断,而是在同一时刻进行判断,也就是说if和后面的if else 或者else其实是同时进行判断的),看红线连接的网络,如果它的等于比较器的逻辑值为1,那么决定了最后一个2选1mux的值必定是和xin0连接的而与前面的结果无关。依次类推,如果它的等于比较器的值为0,那么最后的输出就由前面的逻辑来决定。其实,综合出来这样的结果和我们的设想还是有出入的,一个4选1mux何必如此复杂呢。

下面就看用case语句来做这个4选1mcu吧。

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

case (xsel)

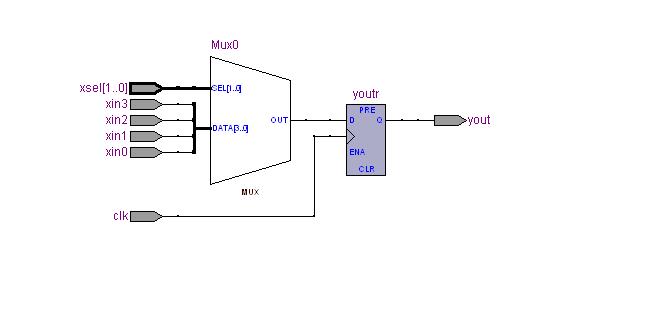

2'b00: youtr RTL视图如下:

呵呵,上面应该就是我们所要的,4选1的mux,一目了然。Case与if的用法还是应该根据具体的情况而定,但是尽量多用case往往会更简化硬件电路。

(由输入xsel来选择输出的路数xin0,xin1,xin2,xin3其一,输出yout)

Ex3:

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

if(xsel == 2'b00) youtr RTL视图如下:

上面的视图里,可以看出有三个等于比较器,然后在触发器前会有三个2选1的选择器。和我们的代码是一样的,第一个if语句的优先级是最高的(这里所谓的优先级最高不是软件意义上的高优先级,由于HDL设计的并行性,判断语句综合后不是先后进行判断,而是在同一时刻进行判断,也就是说if和后面的if else 或者else其实是同时进行判断的),看红线连接的网络,如果它的等于比较器的逻辑值为1,那么决定了最后一个2选1mux的值必定是和xin0连接的而与前面的结果无关。依次类推,如果它的等于比较器的值为0,那么最后的输出就由前面的逻辑来决定。其实,综合出来这样的结果和我们的设想还是有出入的,一个4选1mux何必如此复杂呢。

下面就看用case语句来做这个4选1mcu吧。

input clk;

input xin0,xin1,xin2,xin3;

input[1:0] xsel;

output yout;

reg youtr;

always @ (posedge clk)

case (xsel)

2'b00: youtr RTL视图如下:

呵呵,上面应该就是我们所要的,4选1的mux,一目了然。Case与if的用法还是应该根据具体的情况而定,但是尽量多用case往往会更简化硬件电路。

- FPGA作为协处理器在实时系统中的应用(04-08)

- Virtex-5推动超宽带通信和测距的发展(01-06)

- FPGA异步FIFO设计中的问题与解决办法(01-16)

- 异步FIFO结构及FPGA设计(03-09)

- FPGA单芯片四核二乘二取二的安全系统(03-11)

- 利用FPGA和CPLD数字逻辑实现ADC(06-04)